# INFORMATION

# APPLIKATION

# MIKROELEKTRONIK

## Heft 14:

# C 520 D

# 3-Digit-Analog/Digital-Wandler

veb halbleiterwerk frankfurt (oder) leitbetrieb im veb kombinat mikroelektronik

## KAMMER DER TECHNIK

Vorstand des Bezirksverbandes Frankfurt (Oder), Ebertusstraße 2 Autor : Dr.-Ing. B. Kahl VEB Halbleiterwerk Frankfurt(Oder) Layout : Heinz Schulz Umschlag : Peter Hoffmann

Redaktions-Kollektiv : Heinz Schulz (Vorsitzender) Dipl.-Ing. Peter Grunow, KDT-Beauftragter Dipl.-Ing. Egbert Knopke Dipl.-Ing. Dieter Buttgereit Ing. Wolfgang Richter Dipl.-Wirtsch. Wolfgang Mattke Dipl.-Ing. Hermann Dornfeld

Redaktionsschluß : 15.11.1982

Nachdruck, auch auszugsweise, nur mit Genehmigung des Herausgebers ! Die vorliegende technische Information dient dem Informationsbedürfnis des Schaltungsentwicklers sowie interessierten Technikers im In- und Ausland zu speziellen ausgewählten Erzeugnissen der Halbleiterbauelemente-Industrie der Deutschen Demokratischen Republik. Sie gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion.

Gültige Unterlagen für den Bezug von in den Scheltungen beschriebenen Bauelementen sind allein die Typstanderds, die gültigen Kenndatenblätter oder die im Liefervertrag selbst fixierten Vereinbarungen. Änderungen der Bauelementeeigenschaften, die dem technischen Fortschritt dienen, behält sich der Halbleiterbauelemente-Hersteller vor.

Für die Patentfreiheit der angegebenen Schaltungsvorschläge wird keine Gewähr übernommen. Anfragen und Hinweise, die sich auf Inhalt und Bezug dieser Schrift beziehen, bitten wir an nachstehende Anschriften zu richten:

DDR-Interessenten :

Kammer der Technik Bezirksvorstend Frenkfurt(Oder) <u>1200 Frenkfurt(Oder)</u> Ebertusstraße 2

Interessenten im Ausland :

VEB Halbleiterwerk Frenkfurt(Oder) Leitbetrieb im VEB Kombinat Mikroelektronik Außenstelle Leipzig Werbung und Messen

DDR 7010 Leipzig Messegelände, Halle 17,Kopfbau, II.Etage

## INHALT

## SEITE:

| 1.   | Einleitung                                    | 6  |

|------|-----------------------------------------------|----|

| 2.   | Verfahren der Analog-Digital-Wandlung         | 8  |

| 2.1. | Zählverfahren                                 | 9  |

| 2.2. | AD-Wandlung mit dem Verfahren der sukzessiven | 14 |

|      | Approximation                                 | ÷  |

| 3.   | Kenngrößen und Fehler bei AD- und DA-Wandlern | 21 |

| 3.1. | Auflösung                                     | 21 |

| 3.2. | Kennlinienfehler und Linearität               | 27 |

| 4.   | Allgemeine Kennzeichnung des C 520 D          | 37 |

| 5.   | Funktionsweise des C 520 D                    | 39 |

| 5.1. | Spannungs-Strom-Wandler                       | 42 |

| 5.2. | Komparator                                    | 42 |

| 5.3. | Band-gap-Referenzquelle                       | 43 |

| 5.4. | Oszillator                                    | 45 |

| 5.5. | Teiler                                        | 46 |

| 5.6. | Zähler und Zusatzlogik                        | 45 |

| 5.7. | Kontroll- und Steuerlogik                     | 47 |

| 5.8. | Multiplexer                                   | 48 |

| 5.9. | Ausgangsstufen                                | 49 |

| 6.   | Kennwerte des C 520 D                         | 51 |

| 6.1. | Anschlußbelegung                              | 51 |

| 6.2. | Grenzwerte                                    | 52 |

| 6.3. | Betriebsbedingungen                           | 53 |

| 6.4. | Elektrische Kennwerte                         | 54 |

| 6.5. | Sonderzeichenausgabe                          | 56 |

| 6.6. | Temperaturverhalten                           | 61 |

| Č, t |                                                   |    |

|------|---------------------------------------------------|----|

| 7.   | Applikative Hinweise zum Einsatz des C.520 D      | 64 |

| 8.   | Anwendungsbeispiele für den C 520 D               | 66 |

| 8.1. | Anzeigesysteme                                    | 66 |

| 8.2. | Multiplexsignale                                  | 70 |

| 8.3. | Meßwertspeicherung                                | 71 |

| 8.4. | Betriebsartenumschaltung                          | 75 |

| 8.5. | Vorzeichenausgabe                                 | 76 |

| 8.6. | Ergänzende Baugruppen                             | 77 |

| 8.7. | Standardsignale und ihre Anpassung an den C 520 D | 79 |

| 8.8. | Temperaturmessung                                 | 81 |

| 8.9. | Mikrorechnerkopplung                              | 87 |

| 9.   | Dekoderreihe D 345 bis D 348                      | 91 |

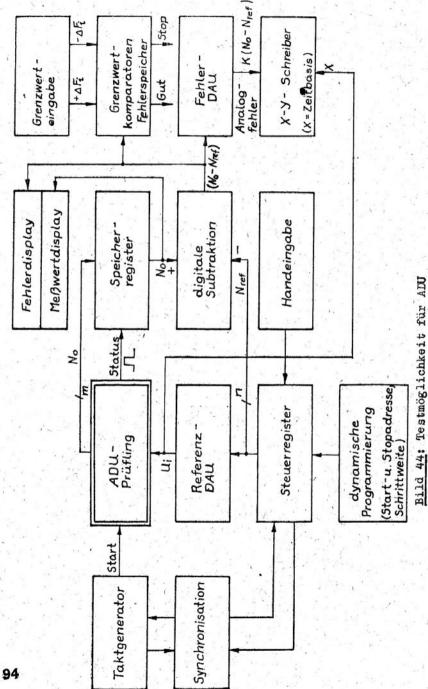

| 10.  | Testmöglichkeiten von Wandlern                    | 93 |

| 11.  | Ligeraturverzeichnis                              | 98 |

#### 1. EINLEITUNG

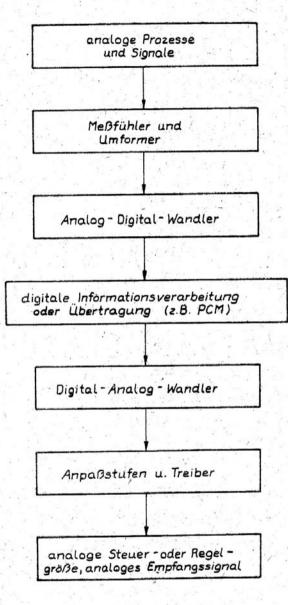

Die Entwicklung in der Industrie ist gegenwärtig durch einen wachsenden Einsatz der Mikroelektronik in der Gerätetechnik gekennzeichnet. Dieser Prozeß erfaßt alle Bereiche und ermöglicht u.a. durch den breiten Einsatz der Mikrorechentechnik gänzlich neue Gerätegenerationen mit wesentlich verbesserten Eigenschaften und Parametern. Dabei spielt die digitale Informationsverarbeitung und- übertragung eine immer stärkere Rolle. Da die Prozesse und zu erfassenden Signale in der Praxis analoger Natur sind, entsteht die Notwendigkeit, über entsprechende Sensoren und Analog-Digital-Wandler den Einstieg in die digitale Signalverarbeitung zu ermöglichen. Andererseits bedingt die rechnergestützte Steuer- und Regeltechnik den Einsatz von Digital-Analog-Wandlern, um nach der digitalen Signalverarbeitung bzw.übertragung mit entsprechenden Anpaßstufen die Stellglieder in technischen Prozessen zu betätigen. Eine prinzipielle Darstellung zeigt Bild 1.

Die Realisierung der Wandler in diskreter Form ist teuer und demzufolge wird in der BMSR-Technik eine Netzstruktur mit analoger Meßwerterfassung und -übertragung, zentraler AD-Umsetzung, digitaler Verarbeitung, DA-Wandlung und analoger Übertragung der Steuer- oder Regelgrößen eingesetzt werden. Mit der Bereitstellung billiger AD- und DA -Umsetzer in monolithischer oder hybrider Form werden diese Bauelemente in wachsendem Maße direkt den Meßstellen und Stellgliedern zugeordnet, so daß die Signalübertragung störsicherer in digitaler Form erfolgen wird.

Mit der Entwicklung des C 520 D ist ein erster Schritt in dieser Richtung erfolgt.

### Bild 1

- Einsatz von AD- und DA-Wandlern-

### 2. VERFAHREN DER ANALOG-DIGITAL-WANDLUNG

An die AD-Wandler werden die unterschiedlichsten Ferderungen gestellt. Im wesentlichen beziehen sie sich auf die Anflösung, die von 6 bit ( $2^6 = 64$  Stufen) bis zu hechpräzisen Wandlern bis 18 bit ( $2^{18} = 262$  144 Stufen) und Umsetzraten von 1 Messung/sec. bis zu ultraschnellen Wandlern mit 100 · 10<sup>6</sup> Messungen/sec. reicht. Für die Realisierung werden verschiedene Verfahren eingesetzt, die im folgenden kurz erläutert werden. Tabelle 1 zeigt einen überschlägigen Vergleich anhand der wesentlichen Kennwerte. In /1/ werden die Verfahren ausführlicher behandelt.

| Verfahren                                                   | maximale<br>Schrittzahl | erforderliche<br>Referenzelement | Geschwindigkeit            | Autward |

|-------------------------------------------------------------|-------------------------|----------------------------------|----------------------------|---------|

| 1. Zähl-<br>methoden                                        | n                       | 4                                | gering                     | gering  |

| 2. Verfsh-<br>ren mit<br>schrittwei-<br>ser Annä-<br>herung | ld n                    | ldn                              | mittlere<br>bis<br>schnell | mittel  |

| 3. Paral.<br>lelverfah-<br>ren                              | 1                       | n                                | sehr<br>schnell            | groß    |

| 4.Kombina-<br>tionen von<br>Verfahren                       | A state of the          | bination werden                  | die unterschied-           | -       |

Tabelle 1: Übersicht zu Verfahren der AD-Wandlung

#### 2.1. Zählverfahren

Zu den seriellen oder Zählverfahren gebören :

- Sägezahnumsetzer (U/t)

- Zwei- und Mehrflankenintegrationsverfahren

- Spannungs-Frequenz-Umsetzer (U/f)

- Charge-Balancing-Verfahren

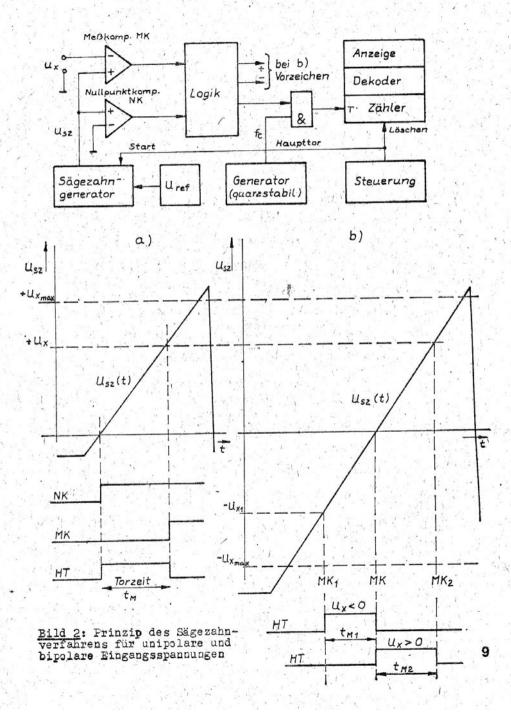

Im Bild 2 ist ein prinzipielles Blockschaltbild mit zwei möglichen Signalverläufen für das Sägezahnverfahren dargestellt.

Die Sägezahnspannung steuert den Nullpunkt- und Meßkomparator. Das Schalten der Komparatoren wird in der Logik in die Torzeit tw = K, • U, wobei K, durch die Steilheit der Sägezahnspannung festgelegt wird, umgesetzt. Die Zahl der Impulse, die während t, durch das Haupttor auf den Zähler gelangen. stellen das Meßergebnis dar. Mit der Taktfrequenz f. und der Steilheit der Sägezahnspannung wird die Umsetzerkennlinie festgelegt. Für bipolare Eingangsspannungen muß die Reihenfolge des Schaltens der Komparatoren in der Logik erfaßt werden. um die Vorzeichenausgabe zu realisieren. Schaltet der Meßkomparator vor dem Nullkomparator, dann ist die Eingangsspannung negativ. Schaltet zuerst der Nullkomparator ist sie positiv. Weil die Genauigkeit des Meßergebnisses durch viele Faktoren ( Konstanz von Umer, Linearität und Steilheit der Sägezahnspannung, Drift'der Komparatoren, Stabilität der Taktfrequenz ) beeinflußt wird, ist die Anwendung auf Systeme mit geringerer Auflösung beschränkt.

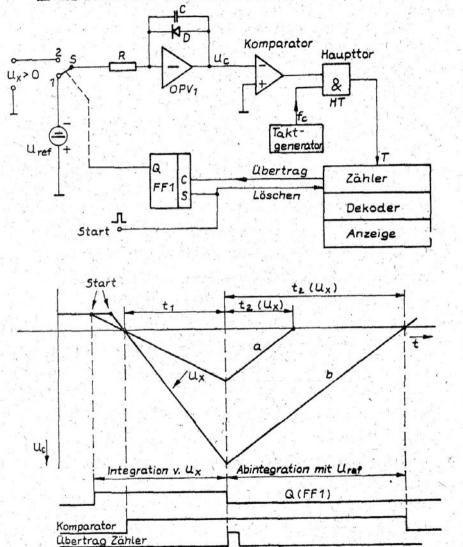

Das Verfahren realisiert keine interne Brummspannungsunterdrückung. Jede überlagerte Störspannung führt an den Schaltpunkten der Kompanatoren zu Fehlern. Im Bild 3 wird die prinzipielle Funktion des Zwei-Flanken-Integrationsverfahrens ( Dual-Slope-Verfahren, Doppelintegrationsverfahren ) gezeigt. Es gehört zu den am häufigsten in der Meßtechnik verwendeten Verfahren.

Mit dem Startimpuls wird FF1 so gestellt, daß der Schalter S die Eingangsspannung zu dem als Integrator beschalteten OPV durchstellt. Gleichzeitig wird der Zähler, in dem das Ergebnis der vorangegangenen Umsetzung steht, zurückgesetzt.

Bild 1: Prinzip des Zwei-Flanken-Integrationsverfahrens

Der Integrationskondensator C wird während  $t_1$  über R aufgeladen. Durchläuft die Integratorspannung U<sub>c</sub> den Nullpunkt, dann schaltet der Komparator und gibt das Tor für die Taktimpulse frei, die im Zähler aufsummiert werden. Gibt der Zähler einen Übertragsimpuls ab, wird FF1 so gesetzt, daß S auf die Referenzspannung umschaltet. Im Zähler steht zu diesem Zeitpunkt die Zahl O (Ausgabe des Übertragers wegen Erreichen des maximalen Zählerstandes N + 1 oder Zwangsrücksetzung bei Erreichen eines festgelegten Wertes ). D.h., die erste Phase arbeitet mit einer festen Zeit  $t_1$ , die von der Übertragsausgabe bzw. dem Zählerumfang und der Taktfrequenz festgelegt wird.

Die Ausgangsspannung am Integrator ergibt sich zu

$$U_{c1} = \frac{Q_{c}}{C} = \frac{1}{R \cdot C} \cdot \int_{x(t)}^{t_{1}} U_{x(t)} \cdot dt$$

Für Ux = konstant löst sich die Gleichung zu

$$\mathbf{U}_{c1} = \frac{\mathbf{U}_{x} \cdot \mathbf{t}_{1}}{\mathbf{R} \cdot \mathbf{C}}$$

Die Integrationszeit t<sub>1</sub> wird meist so gewählt, daß sich ein ganzzahliges Vielfaches der Netzfrequenz ergibt, um eine möglichst gute Brummspannungsunterdrückung zu erreichen.

In der zweiten Phase wird die Kondensatorladung mit einem Konstantstrom abgebaut bis der Komparator das Erreichen von U<sub>c</sub> = O V durch Sperren des Haupttores und Beenden der Zählung signalisiert. Entsprechend der obigen Überlegung ergibt sich für den Ladezustand nach t<sub>2</sub> :

$$U_{c2} = \frac{1}{R \cdot C} \cdot \int_{0}^{t_{2}} U_{ref} \cdot dt$$

$$U_{c2} = \frac{U_{ref} \cdot t_{2}}{R \cdot C}$$

Durch Gleichsetzen erhält man

$$t_2 = \frac{U_x}{U_{ref}} \circ t_1$$

D.h., die Werte für R und C fallen heraus. Der Zählerstand nach to ergibt sich zu

$$Z = t_2 \cdot f_c = \frac{U_x}{U_{ref}} \cdot t_1 \cdot f_c$$

Die Zeit t<sub>1</sub> wird durch den Zählerumfang oder vorgewählten Zählerstand N und die Taktfrequenz f<sub>c</sub> festgelegt.

$$t_1 = \frac{1}{f_c}$$

Setzt man das in die Gleichung für den Zählerstand Z ein, ergiht sich

$$Z = \frac{U_{x}}{U_{ref}} + N$$

Das bedeutet, daß die Tektfrequenz nicht absolut sondern nur während  $t_1 + t_2$  konstant zu halten ist. Damit genügen in den meisten Fällen einfache Generatoren den Anforderungen. Außerdem ist zu sehen, daß die Referenzspannungskonstanz im wesentlichen die Genauigkeit bestimmt.

Als Nachteil ist die verhältnismäßig lange Umsetzzeit zu nennen, so daß nur Signale, die sich langsam ändern verarbeitet werden können. Das Verfahren ist für Wandler mit Genauigkeiten bis 13 ... 14 bit bzw. 4<sup>1</sup>/2 Dekaden einsetzbar.

Erweiterungmzu diesem Verfahren stellendie 3- und 4-Flankenintegrationsverfahren dar. Durch das Zufügen von weiteren ein oder zwei Integrationsphasen, bei denen z.B. die eigenen Offsetgrößen des Wandlers analog oder digital zwischengespeichert werden, erhält man AD-Umsetzer mit automatischer Nullpunktkorrektur. Bei jedem Meßzyklus wird dabei die echte Differenz zwischen dem Meßwert und der darin enthaltenen Offsetgröße gebildet.

Mit dem Charge-Balancing-Verfahren ( Ladungsausgleichsverfahren) können Umsetzer mit geringen Anforderungen an die Bauelemente realisiert werden. In den letzten Jahrgängen der " rfe " und " Nachrichtentechnik " sind dazu einige Artikel erschienen / 2, 3, 4/.

2.2, AD-Wandlung mit dem Verfahren der sukzessiven Approximation

14

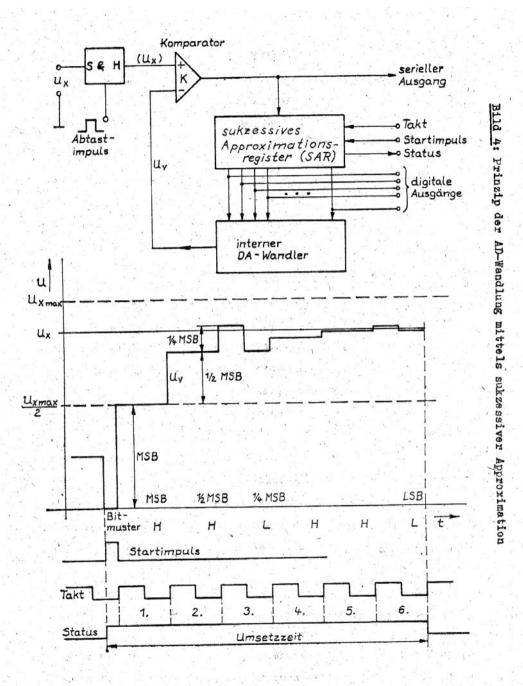

Für schnelle und mittelschnelle Umsetzer eignen sich serielle Wandler nicht. Einen Kompromiß hinsichtlich Aufwand und Geschwindigkeit stellt die sukzessive Approximation (schrittweise Annäherung ) dar /5,6/.

Der Wandler besteht aus einem Komparator, einem internen DA-Wandler und einer sukzessiven Approximationslogik. Die vorgeschaltete Sample & Hold-Stufe ist dann erfoderlich , wenn  $U_x$  sich während der Umsetzzeit um  $2 \ 1/2$  LSB ändert. ( LSB 2 least significant bit 2 kleinste unterscheidbare Amplitudenstufe; MSB 2 most significant bit 2 Stufe mit der höchsten Wertigkeit =  $U_{xmax}/2$  ). Mit dem Startimpuls wird das Appreximationsregister so gestellt, daß das MSB des DAU gesetzt wird und sich damit das Vergleichssignal  $U_y$  auf

U<sub>xmax/2</sub> einstellt.

'16

Der Komparator vergleicht  $U_x$  und  $U_y$ . Da für das MSB gilt:  $U_y < U_x$  im gezeichneten Fall, liegt der Ausgang auf H, dann wird mit der nächsten H/L-Flanke des Taktes das MSB verriegelt, d.h., es bleibt gesetzt. Mit dem zweiten Taktimpuls wird MSB/2 eingeschaltet. Der Komparator vergleicht jetzt MSB +  $1/2 \cdot MSB < U_x$ .

Der Komparatorausgang bleibt auf H liegen. Die Stufe 1/2 MSB wird durch das SAR verriegelt - bleibt gesetzt. Mit dem dritten Taktimpuls wird zu den beiden höchstwertigsten Bits 1/4MSB dazugeschaltet. Es ergibt sich : MSB + 1/2 MSB + 1/4 MSB

>U<sub>x</sub>, d.h., mit der fallenden Taktflanke im dritten Takt wird im SAR der Eingang des DAU zurückgesetzt, da der Komparatorausgang auf L liegt. Dieser Vorgang wiederholt sich, bis das LSB abgearbeitet ist. Das Statussignal wird im SAR erzeugt. Es zeigt das Arbeiten des Wandlers mit H am Ausgang an.

Dieses Wandlungsprinzip kann sowohl hardwaremäßig als auch im Zusammenspiel mit einem Mikrorechner realisiert werden, wobei die Approximationslogik durch ein Programm ersetzt wird. Der serielle Ausgang eignet sich in Verknüpfung mit dem Taktsignal und einer entsprechenden Synchrönisation zur leitungssparenden Übertragung der digitalen Informationen. Das Verfahren ist gegenüber Störspannungen am Eingang während der gesamten Umsetzzeit empfindlich, wenn U<sub>stör</sub> t<sup>1</sup>/2 · LSB wird.

Mit der Bereitstellung des DAC 32, einem universellen 12 bit-DAU, vom Kombinat Keramische Werke Hermsdorf bietet sich hier für die wesentlichste Baugruppe eines 12 bit-DAU, der das Verfahren der sukzessiven Approximation einsetzt, eine Realisierung an.

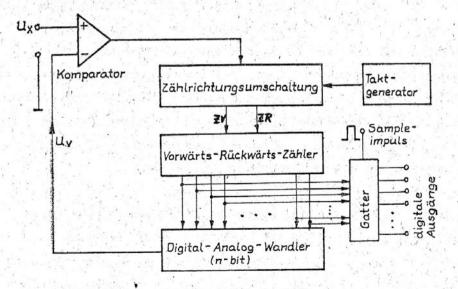

Im folgenden soll ein Verfahren beschrieben werden, das eher zum Abschnitt 2.1. gehört, weil es sich um ein serielles Verfahren handelt. Die Struktur dieses Wendlertyps hat aber sehr viel Ahnlichkeit mit der sukzessiven Approximation.

Die Logik wird durch einen Vorwärts-Rückwärts-Zähler ersetzt.

Bild 5: Folge- oder Tracking - A D U

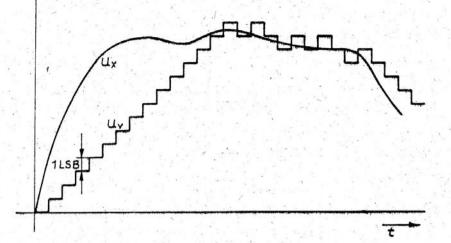

Der Zähler wird vorwärts getaktet, d.h., die Ausgangsspannung des DAU U<sub>v</sub> steigt, bis U<sub>v</sub> > U<sub>x</sub> wird. Der Komparator kippt um und der Zähler wird rückwärts gezählt bis U<sub>v</sub> < U<sub>x</sub> ist. Die Anstiegsfähigkeit von U<sub>v</sub> wird durch die Höhe eines LSB und die Taktfrequenz bestimmt. Ohne weiteren Steuermechanismus folgt U<sub>v</sub> der Eingangsspannung. Um ein stehendes Bitmuster zu gewinnen, werden die Zählerausgänge über Gatter und einen Sampleimpuls abgefragt. Es besteht aber auch die Möglichkeit, über eine Sample & Hold-Schaltung U<sub>x</sub> abzufragen und zu speichern.

Um zu verhindern, daß bei konstanter Eingangsspannung das LSB ständig zwischen L und H wechselt, gibt es zwei Möglichkeiten. Entweder man versieht den Komparator mit einer Schalthysterese von  $\pm$  <sup>1</sup>/2 LSB, oder es wird ein DA-Wandler verwendet, der eine um 1 Bit höhere Auflösung besitzt als digitale Ausgänge herausgeführt sind.

11

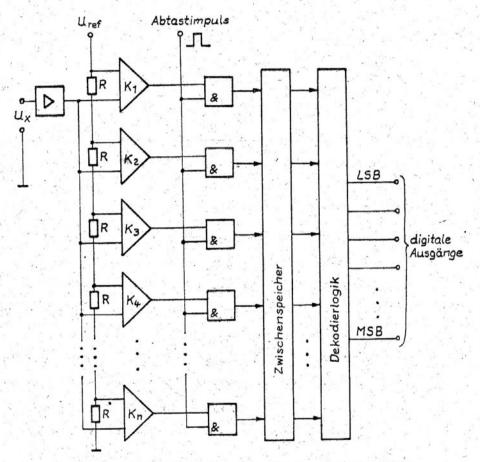

Ein besonders schnelles Umsetzverfahren wird mit Parallelwandlern realisiert. Sie werden auch als Flash-Converter bezeich-

Bild 6: Blockschaltbild eines Parallelumsetzers /1/

Damit werden Umsetzraten bis 100 MHz und Auflösungen bis 9 bit (= 512 Amplitudenstufen) realisiert. Diese Wandler sind praktisch nur monolithisch oder hybrid zu verwirklichen, da die erforderliche Bauelementezahl sehr groß ist. Für einen Wandler mit m bit sind 2<sup>m</sup> - 1 Referenzelemente und Komparatoren erforderlich. Ein 8 bit ADU hat 255 Komparatoren. Die Referenzspannung wird mittels Teilerkette von 2<sup>m</sup> - 1 Widerständen so geteilt, daß die entstehenden Referenzwerte den einzelnen Stufenhöhen der Kennlinie entsprechen. Werden identische Widerstände in der Kette verwendet, so ensteht eine lineare Kennlinie. Mit unterschiedlichen Dimensionierungen für die Widerstände ist jede Art von nichtlinearer Kennlinie möglich. Das Eingangssignal wird über den Trennverstärker, an dessen Stelle auch eine Abtastschaltung verwendet werden kann. , an die anderen Eingänge aller Komparatoren gelegt. Bei jeder Umsetzung liegen die Ausgänge der Komparatoren K, bis K, auf H und die Ausgänge der restlichen Komparatoren  $K_{x+1}$  bis  $K_{n-1}$ auf L. Im Bild 6 nach /1/ wird die Abtastung digital mit den 2<sup>m</sup> -1 Gattern realisiert.

Nach einer Zwischenspeicherung wird in der Dekodierlogik das Digitalwort mit m bit gebildet. Da die Verzögerungszeiten der vier Baugruppen, Komparatoren, Gatter, Zwischenspeicher und Dekodierlogik sehr klein gehalten werden können, werden diese hohen Umsetzraten erreicht. Diese Wandler benötigen bis auf die Abtastung keine Steuerung. D.h., bei einer Änderung von U<sub>x</sub> schalten die Komparatoren automatisch auf den neuen Wert. Es ist auch möglich, die Abtastung und Zwischenspeicherung nach der Dekodierlogik anzuerdnen.

Das verringert die erforderliche Bauelementezahl erheblich. Das trifft auch zu, wenn eingangsseitig eine Abtastschaltung für U., verwendet wird.

## 3. KENNGRÖßEN und FEHLER bei AD- und DA- WANDLERN

Bevor die Darstellung des C 520 D erfolgt, erscheint es sinnvoll, die wesentlichen Parameterdefinitionen von AD- und DA-Wandlern zu erläutern, da es erfahrungsgemäß Unklarheiten bei einigen Kennwerten gibt und einige sowohl auf AD- als auch auf DA-Wandler zutreffen. Umfangreiche Darstellungen sind in /7/ und /8/ enthalten, wobei das IEC-Dokument /7/ die in Zukunft international übliche Festlegung der Definitionen und Formelzeichen enthält, die sich für die wesentlichen Kennwerte kaum ändern werden, obwohl das Dokument noch zur Diskuesion steht. Die verwendeten Kurzzeichen für den C 520 D stimmen nicht in jedem Fall mit den in /7/ enthaltenen überein.

#### 3.1. Auflösung

Sie wird in bit bzw. für dekadische Wandler in Digit angegeben

Binärwandler:

| Stufenzahl              | Auflösung ( % vom Endwert )                                                             |

|-------------------------|-----------------------------------------------------------------------------------------|

| 2 <sup>6</sup> = 64     | 1,6 %                                                                                   |

| 2 <sup>8</sup> = 256    | 0,39 %                                                                                  |

| $2^{10} = 1024$         | 0,098 %                                                                                 |

| 2 <sup>12</sup> = 4096  | 0,024 %                                                                                 |

| 2 <sup>14</sup> = 16384 | 61 ppm *                                                                                |

| 2 <sup>16</sup> = 65536 | 15 ppm *                                                                                |

|                         | $2^{6} = 64$<br>$2^{8} = 256$<br>$2^{10} = 1024$<br>$2^{12} = 4096$<br>$2^{14} = 16384$ |

| Digit             | Stufenzahl | Auflösung ( % vom Endwert ) |

|-------------------|------------|-----------------------------|

| 21/2              | 200        | 0,5 %                       |

| 3 .               | 1000       | 0,1 %                       |

| 31/2              | 2000       | 0,05 %                      |

| 4                 | 10000      | 0,01 %                      |

| 4 <sup>1</sup> /2 | 20000      | 0,005 %                     |

\* ppm 2 Parts per million

## Tabelle 2: Stufenzahl und Auflösung von Binär- und BCD-Wendlern

Die Auflösung für sich gesehen kann ein falsches Bild von der Güte des Wandlers vermitteln. Die Linearitätsfehler sind häufig größer als die Auflösung und sind unbedingt zu berücksichtigen.

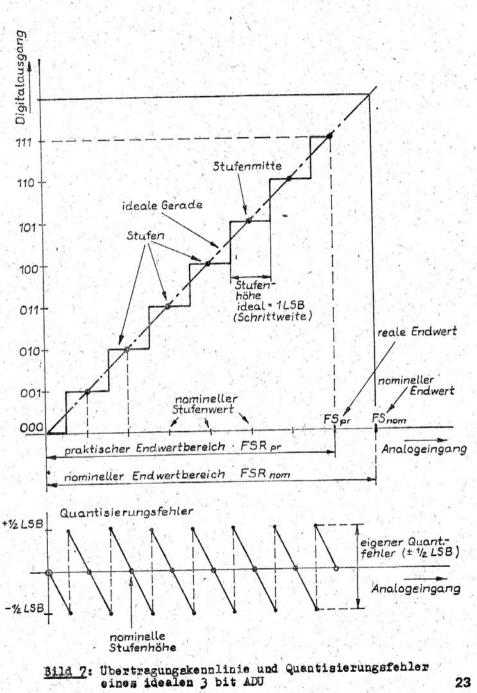

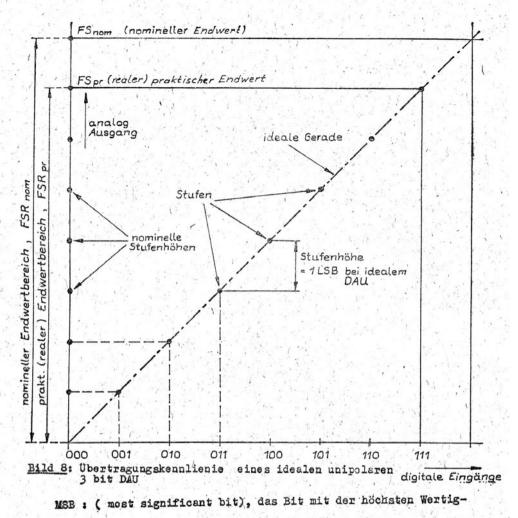

Im Bild 7 ist die Übertragungskennlinie eines idealen 3 bit ADU und im Bild 8 die Wendlerkennlinie eines idealen 3 bit DAU dargestellt. Die wesentlichen Größen sind eingezeichnet.

LSB : ( least significant bit), 1 LSB entspricht der analogen Auflösung und berechnet sich zu

$$1 \text{ LSB} = \frac{\text{FSR}_{\text{pr}}}{2^{n} - 1} = \frac{\text{FSR}_{\text{nom}}}{2^{n}}$$

n = Bitzahl des Wandlers

keit

$$1 \text{ MSB} = \frac{\text{FSR}_{nom}}{2} = \frac{\text{FSR}_{pr}}{2} + 4 \text{ LSB}$$

LSD : ( least significant digit), die Einerstelle ( 10<sup>0</sup>) einer Dezimalzahl

MSD : ( most significant digit), die höchstwertigste Dekade einer Dezimelzahl z.B. von 392 2 MSD = 3 x 10<sup>2</sup> Der Quantisierungsfehler ist jedem AD-Wandler eigen und beträgt ± 7/2 ISB, Der Verlauf wird im Bild 7 gezeigt.

## Ein- oder Ausgangsspannungsbereich (FSR)

Die Erklärung der Größen FS ( full scale ) = Endwert, FSR ( full scale range ) mit der Unterscheidung nominell und praktisch geht aus Bild 7 und 8 hervor.

FS kennzeichnet den Endwert der Ein- oder Ausgangsspannung und FSR den Ein- oder Ausgangsspannungsbereich. FS(R)<sub>pr</sub> den unterscheiden sich um 1 LSB. Für einen idealen binären DAU gilt :

$FSR_{pr} = (2^n - 1) \cdot Stufenhöhe$

$FSR_{nom} = 2^n \cdot Stufenhöhe$

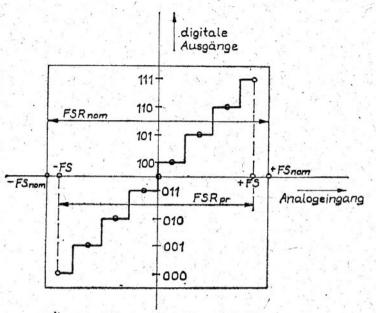

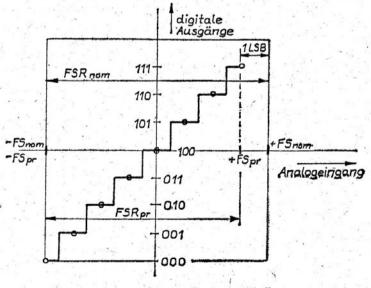

Für einen ADU ist der Begriff Stufenhöhe durch Schrittweite zu ersetzen. Diese Bezeichnung gilt für unipolare Ein- oder Ausgangsspannungen. Für Wandler mit bipolren Ein- oder Ausgängen ist der positive (FS<sub>+</sub>) und der negative (FS<sub>-</sub>) Endwert zu definieren. Für nullsymmetrischen Betrieb gilt:  $FS_{+} = FS_{-} \cdot Im$  Bild 9 wird der um Null symmetrische und unsymmetrische Betrieb mit der Verschiebung der Kennlinie um 1/2 LSB gezeigt.

#### Bild 9: Abgleichvarianten für bipolare Ein- oder Ausgangsspannungen

a) symmetrischer Betrieb um Null

b) unsymmetrischer Betrieb, um Null

# 3.2. Kennlinienfehler und Linearität

Im folgenden sollen die verschiedenen Fehlererten von Wandlern näher erläutert werden.

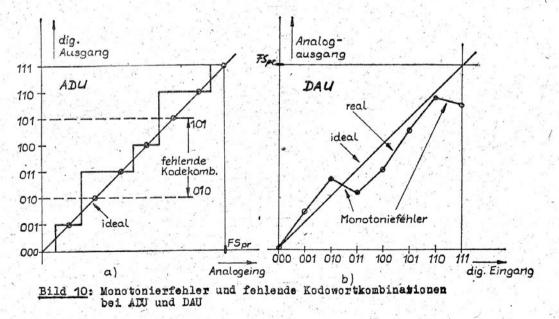

Monotonie : Sie kennzeichnet den Verlauf der Ausgangsspannung eines DA-Wandlers. Monotonie verlangt, daß mit steigender digitaler Eingangsbit-Kombination die Ausgangsspannung ansteigt. Jedes Absinken der Kennlinie ist ein Monotoniefehler.(Bild 10b). Ein Wandler mit einem Linearitätfehler von ± 1/2 LSB ist zwangsläufig monoton.

Fehlkodes : Sie kennzeichnen das Verhalten eines AD-Wendlers, bei dem mit der Erhöhung der Eingengsspannung bestimmte Kodekombinationen übersprungen werden. Dieser Fehler kann z.B. beim Über- oder Unterschreiten von Temperaturwerten auftreten und bei normaler Raumtemperatur nicht nachweisbar sein. (Bild 10 a) Sie entsprechen Monotoniefehlern bei DA-Wandlern.

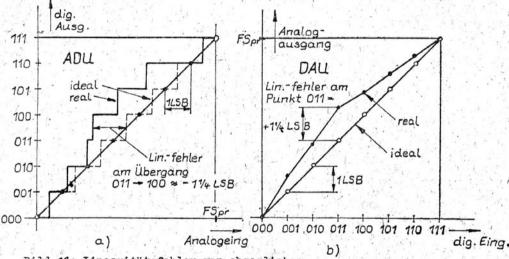

Bild 11: Linearitätsfehler von abgeglichenen ADu und DAU

> Linearität : Sie kennteichnet die Abweichung der realen Wandlerkennlinie von der idealen. Bild 11 a und 11 b zeigen entsprechende Kennlinienverläufe für abgeglichene 3 bit ADU und DAU. Die Angabe erfolgt in der Regel in x LSB oder in x % von FS ( x % vom Endwert). Dabei ist zu beachten, daß n-bit Wandler mit einem Linearitätsfehler von  $> \pm 1/2$  LSB Monotonfefehler aufweisen können und genaugenommen keine n-bit sondern nur (n - 1) oder ( n- 2) bit-Wandler sind. (Kurzzeichen für Linearitätsfehler laut IEC = E<sub>1</sub> ( error linearity)

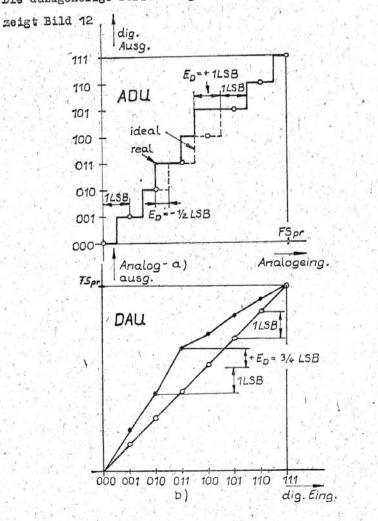

Differentielle Nichtlinearität : (Kurzzeichen laut IEC für den differentiellen Nichtlinearitätsfehler =  $E_D$ ). Damit wird das Übergangsverhalten der Kennlinie von der Stufe  $m \rightarrow m + 1$  bzw.  $m \rightarrow m - 1$  beschrieben.

> $E_D$  = reale Stufenhöhe (Schrittweite) - 1 LSB  $E_D$  = reale Stufenhöhe (Schrittweite) -  $\frac{FSR_{nom}}{2^n}$

Die dazugehörige Darstellung für einen 3 bit ADU und DAU

Bild 12: Derstellung der differentiellen Nichtlinearität von ADU und DAU Für alle Wandler, die mit einem internen DA-Wandler arbeiten, sind die Stellen um das MSB, <sup>1</sup>/2 MSB, <sup>1</sup>/4 MSB und Kombinationen der höchstwertigsten Stufen besonders kritisch hinsichtlich dieser Fehlerart.

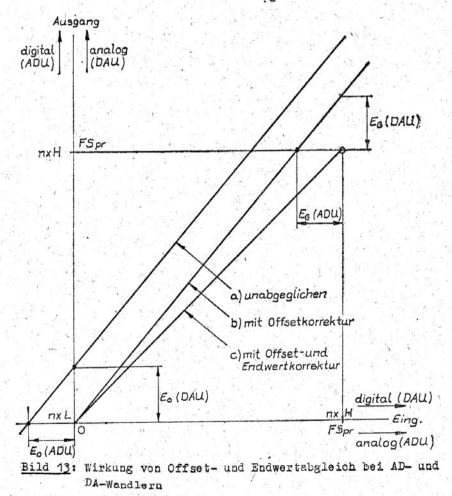

Der Einsatz eines Wandlers erfodert in der Regel die Koorektur von zwei Fehlern :

- Offset- oder Nullpunktfehler Eo

- Verstärkungs-, Steilheits- oder Endwertfehler E<sub>G</sub>

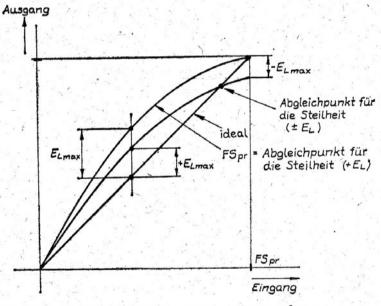

Im unabgeglichenen Zustand weist der Wandler beide Fehler auf (a). Zuerst erfolgt mit  $U_i = 0$  V oder n x O an den Digitaleingängen die Nullpunktkorrektur (b) und danach der Endwertabgleich ( c = ideal). Da die Kennlinien in der Regel neben den beiden Fehlern  $E_0$  und  $E_G$  einen Linearitätsfehler  $E_L$  aufweisen, z.B. einen " Bauch " über dem gesamten Kennlinienbereich kann es zur Minimierung des gesamten Umsetzfehlers günstig sein, den Abgleich zwar am Nullpunkt aber nicht am Kennlinienende (FS) vorzunehmen. Im Bild 14 ist dieser Abgleich skizziert.

Bild 14: Wandlerabgleich zur Minimierung des Linearitätsfehlers E<sub>L</sub>

Statt eines rein positiven Linearitätsfehlers erhält man auf diese Weise einen positiven und negativen Fehleranteil. Diese Methode wird auch dann angewendet, wenn in einem ganz bestimmten Kennlinienbereich präzise gemessen werden soll. Umsetzzeit : Sie gibt an, wie lange der AD-Wandler benötigt, um eine vollständige Meßwertumsetzung bis zur Ausgabe des Digitalwortes vorzunehmen. Für Wandler mit sukzessiver Approxination beginnt die Zeit mit der Vorderflanke des Startimpulses und endet mit der Rückflanke des Statussignals. Für langsame ADU wird meistens die Umsetzrate in Messungen/sec. angegeben. Dabei ist nicht in jedem Fall

Umsetzrate =

#### Umsetzzeit

da Wandler mit synchronisierter Auslösung der Meßwertumsetzung Totzeiten aufwelsen können.

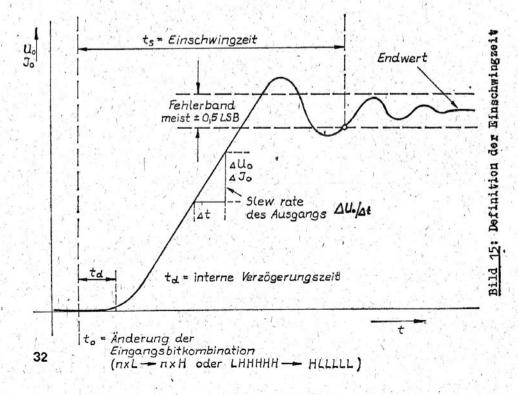

Einschwingzeit ( $t_s$  = settling time) : Sie ist ein Maß für die Geschwindigkeit eines DA-Umsetzers und gibt die Zeit an, die der Wandler benötigt, um nach dem Anlegen einer digitalen Eingangsbitkombination den Strom- oder Spannungsausgang des Wandlers auf den neuen Wert  $x \pm \frac{1}{2}$  · LSB einzustellen.

Die Einschwingzeit kann für zwei verschiedene Sprungsfunktionen angegeben werden.

- ☆ Änderung um den maximal möglichen Ausgangshub, d.h., Änderung der Digitaleingänge von n x L auf n x H

- Anderung des Ausgangshubes um 1 LSB an der Stelle des MSB IHHHHHH -> HILILLL ( MSB - 1 LSB -> MSB)

Die zweite Definition liefert in der Regel etwas kürzere Einschwingzeiten.

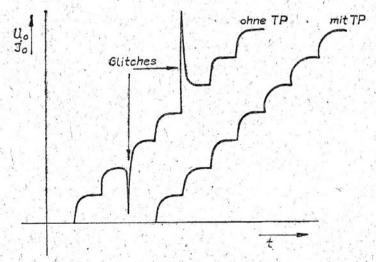

Glitch : Störnadeln im Ausgangssignal eines DAU, die durch unterschiedliche Ein- und Ausschaltzeiten z.B. der Stromquellenumschalter erzeugt werden. Je nachdem, welche der beiden Zeiten länger oder kürzer ist, entstehen positive oder negative Störnadeln.

#### <u>Bild 16</u>: Ausgangstreppenfunktion eines DAU mit und ohne Glitches

Verursachen diese Glitches Störungen in nachfolgenden Systemen, dann kann z.B. der Ausgangs-OPV des Wandlers als Integrator beschaltet werden, der die Störungen eliminiert.

Temperaturverhalten : Der Temperaturkoeffizient (TK) wird in der Regel für drei Kennwerte des Wandlers angegeben

- TK vom Nullpunkt (Offset) in /uV/°C oder in ppm/°C TK(E<sub>0</sub>)

- TK vom Endwert (Verstärkung) in ppm/°C bezogen auf den Endwert TK(E<sub>C</sub>)

- TK des Linearitätsfehlers TK (ET.) in ppm/°C

Bei Wandlern mit automatischer Nullpunktkorrektur (auto-zero) kann die Offsetdrift in den meisten Fällen vernachlässigt werden.

Kodearten : 12 Low, H2 high

Binärkode : Nullpunkt : n x L

Endwert : n x H

Ausgangsspannung: unipolar

- Komplementär-Binärkode: CB oder CBIN

Nullpunkt : n x H

Endwert : n x L

Ausgangsspannung : unipolar

Offset-Binärkode : OB oder OBIN

Ausgangsspannung bipolar (entsprechend Bild 9 a)oder 9 b)) n x L liefert -FS<sub>pr</sub> n x H liefert +FS<sub>or</sub> Komplementär-Offset-Binärkode: COB oder COBIN Ausgangsspannung : bipolar n x H liefert -FS<sub>pr</sub> n x L liefert +FS<sub>pr</sub>

Roll over Fehler : Eine Angabe für AD-Umsetzer mit bipolaren Eingangsspannungsbereichen. Fehler, der beim Umpolen der Eingangsspannung in der Anzeige entsteht.

Beispiel : abgeglichen bei U<sub>1</sub> = +1,999 V umpolen ergibt U<sub>1</sub> = -1,999 V angezeigt werden z.B. -1,997 V Roll over Fehler = 2 mV = 2 LSB

Betriebsspannungsunterdrückung : SVR ( supply voltage rejection)

SVR (dB) = 20 · lg

$$\frac{\Delta \sigma_s}{\Delta Fs_{pr}}$$

Dieser Kennwert wird auch häufig als Empfindlichkeit gegenüber Betriebsspannungsänderungen angegeben und lautet dann

> prozentuale Änderung von  $FS_{pr}$  pro 1 Prozent Betriebsspannungsänderung  $\left[ \% \Delta FS_{pr} / \% \Delta U_s \right]$

Gleichtaktunterdrückung : CMR ( common mode rejection )

$$CMR (dB) = 20 \cdot \lg \frac{\Delta U_{CM}}{\Delta \text{ Anzeige}}$$

Bei AD-Wandlern werden beide Eingänge kurzgeschlossen (Anzeige = O) und um U<sub>CM</sub> gegenüber Betriebsspannungsmasse angehoben oder abgesenkt. Die Änderung der Anzeige ist der Bezugswert. Dabei ist zu beachten, daß bei integrierenden ADU der Gleichtaktbereich durch die Betriebsspannung, den maximalen Hub am Integrationskondensator und den notwendigen Arbeitsbe- 35 bereich der Schaltung bestimmt ist. D.h., durch die Festlegung von U<sub>s</sub> und der externen Bauelemente kann Einfluß auf den zulässigen Gleichtakteingangsspannungsbereich genommen werden.

Am Schluß der Begriffserläuterung sollen noch zwei oft auftauchende. Bezeichnungen genannt werden.

Nichtlineare AD- und DA-Wandler :

Das sind Wandler, mit speziellen gekrümmten oder stückweise linearen zusammengesetzten Kennlinien wie sie z.B. in der PCM - Technik zur Digitalisierung von Sprachsignalen eingesetzt werden (Kompanderkennlinien), um über einen bestimmten Dynamikbereich ein etwa konstantes Signal-Rausch-Verhältnis zu realisieren.

# Multiplizierende DA-Wandler :

33

Diese DA-Umsetzer haben einen Referenzspannungseingang, dessen U<sub>ref</sub> in weiten Grenzen variiert werden kann. Die Ausgangsspannung ergibt sich zu

Un = Uref . N ( N = angelegtes Digitalwort)

Je nach Auslegung des Wandlers werden sie nach 1-, 2- oder 4-Quadranten-Multiplikation unterschieden. Für NF-Signale sind sie als digital steuerbar Dämpfungssteller einsetzbar.

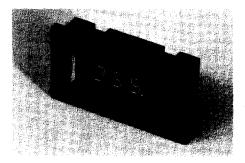

### 4. ALLGEMEINE KENNZEICHNUNG des C 520 D

Der C 520 D des VEB Halbleiterwerk Frankfurt(Oder) ist der erste monolithische Analog-Digital-Wandler, der in der DDR gefertigt wird. In ihm sind alle wesentlichen Baugruppen eines Zwei-Flanken-Integrationsumsetzers enthalten. Er besitzt eine Auflösung von 3 Digit, das entspricht 1000 Stufen. Der Wandler zeichnet sich durch einen hohen funktionellen Integrationsgrad, einen geringen Leistungsverbrauch bei nur einer Betriebsspannung, die TTL-Bedingungen genügt, und vielseitige Einsatzmöglichkeiten aus. Die Funktion des Dual-Slope-Verfahrens wurde im Abschnitt 2. bereits erläutert. Die dort genannten Vor- und Nachteile treffen natürlich auch auf den C 520 D zu.

- Störspannungsunterdrückung in Abhängigkeit von der Signalintegrationszeit

- relative Unempfindlichkeit gegenüber Taktfrequenzschwankungen, da nur Kurzzeitstabilität während der AD-Wandlung zu fordern ist

- geringe Umsetzrate, die aber für meßwertanzeigende Systeme ausreicht.

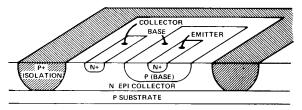

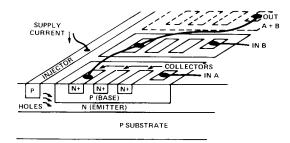

Die Herstellung des C 520 D erfolgt mit einer I<sup>2</sup>L-Technologie. Diese Technologie eignet sich besonders für die Kombination von analogen und digitalen Funktionselementen auf einem Chip und zur Realisierung leistungsarmer Bauelemente. /9, 10/ Der C 520 D ist ein LSI-Bauelement mit mehr als 1200 Funktionselementen, die etwa zu 75 % dem Digitalteil und zu 25 % dem Analogteil zuzuordnen sind.

Der Wandler wurde speziell für meßwertanzeigende Systeme konzipiert, ist aber auch für meßwertverarbeitende Systeme z.B. auf der Basis von Mikrorechnern geeignet, da er über gemultiplexte BCD-Ausgänge verfügt. Er ist für den Einsatz in der BMSR-Technik unter prozeßnahen Bedingungen auf Grund seiner Eigenschaften geeignet. Mit wenigen externen Bauelemente ist es möglich, ein digital anzeigendes Meßgerät für einen Bereich aufzubauen, wenn als Eingangsgröße Standard-BMSR-Signale zur Verfügung stehen. Er eignet sich als Ersatz von elektromechanischen Meßwerken. D.h., die Präzisionsmechanik kenn durch wesentlich einfachere und billigere Montagetechnologien ersetzt werden.

Der C 520 D besitzt eine interne Referenzspannungs- bzw. Stromquelle und eine Taktversorgung. Dadurch wird der Einsatz des Wandlers wesentlich erleichtert. Er setzt eine Eingangsspannung von  $U_i = -99$  mV bis  $U_i = +999$  mV mit einer Auflösung von 1 mV in dekadenweise gemultiplexte BCD-Worte um. Sein Linearitätsfehler beträgt maximal 0,1 % vom Meßwert  $\pm$  1 Digit. Der Wandler verfügt über eine automatische Polaritäts- und Überlauferkennung. Es erfolgt eine entsprechende Ausgabe von Sonderzeichen, um diese Zustände nach außen zu signalisieren. Für die Meßwertverarbeitung ist besonders die Wahl zwischen drei verschiedenen Betriebsarten von Interesse.

- langsame Wiederholrate

- schnelle Wiederholrate

- Hold-Betrieb (digitale Speicherung)

In Hold-Betrieb wird der zuletzt aufgenommene Meßwert gespeichert und ständig ausgegeben. Die Versorgung des Schaltkreises erfolgt mit einer Betriebsspannung von  $U_S = +5 V \pm 10 \%$ und paßt damit zu TTL-Systemen ( $U_S = +5 V \pm 5\%$ ). Sein Leistungsverbrauch ist gering. Die externe Bauelementezahl wird besonders gering, wenn ein Umsetzer mit dreistelliger LED-Anzeige mit gemeinsamer Anode verwendet wird.

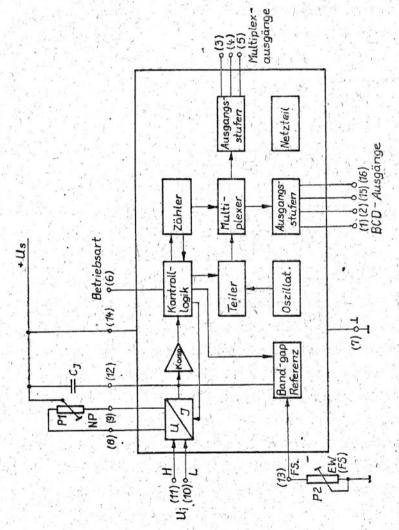

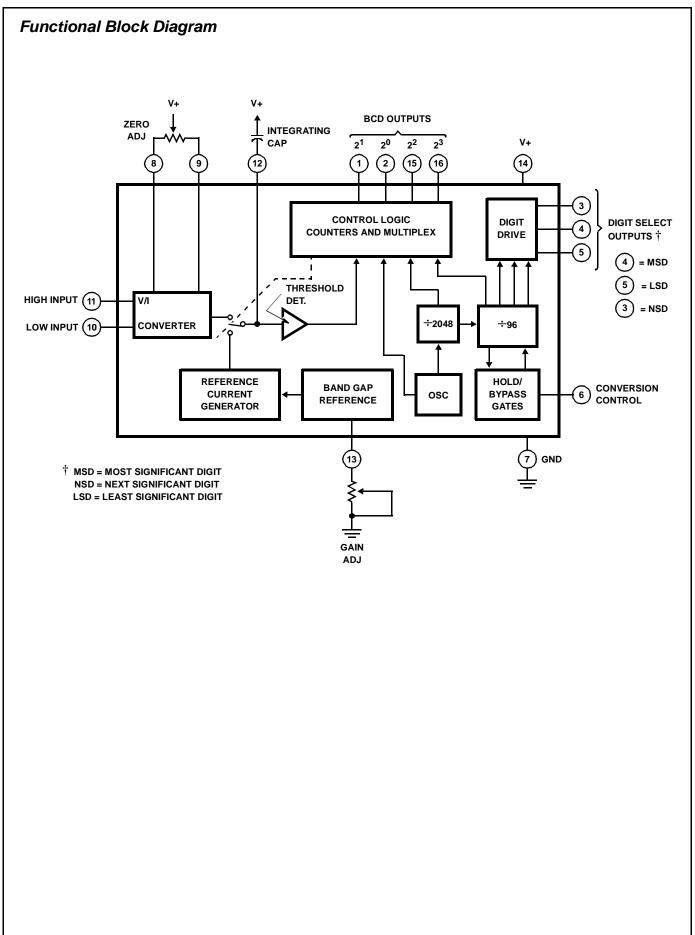

#### 5. FUNKTIONSWEISE DES C 520 D

Der Wandler arbeitet nach dem Prinzip der Zwei-Flanken-Integration. Nach der Herstellung des Ausgangszustandes des Systems wird während einer festen Meßzeit t, das zu messende Eingangssignal aufintegriert. Diese Zeit ist in der Regel durch den Zählumfang des internen Zählers und die Taktfrequenz f. festgelegt. In der zweiten Phase wird die aufgeladene Integrationskapazität durch einen Referenzstrom entgegengesetzt der Polarität bis zum Erreichen des Referenzpegels am Komparator entladen. Die dazu erforderliche Zeit ist proportional zum Eingangssignal. Da beide Phasen durch die gleiche Taktfrequenz ausgezählt werden, verbleiben nur die Schwankungen innerhalb des gesamten Meßzyklus als Fehler im Gegensatz zu den Spannungs-Zeit-Umsetzern nach dem Sägezahnverfahren, bei denen der Absclutwert der Taktfrequenz die Genauigkeit der Wandlung beeinflußt. Um eine Brummspannungsunterdrückung für 50 Hz zu realisieren, werden bei integrierenden AD-Wandlern der Zählerumfang und die Taktfrequenz so gewählt, daß die Integrationszeit für die Eingangsspannung n x 20 ms beträgt und damit genau eine bzw. n über-

Bild 17: Blockschaftbild des C 520 D

lagerte 50 Hz-Schwingungen erfaßt werden. Beim C 520 D wird das Eingangssignal etwa über 1 ms aufintegriert. Damit hat das Bauelement verfahrenstechnisch keine Brummspannungsunterdrückung.

Das Blockschaltbild des C 520 D ist im Bild 17 enthalten. Er besteht im wesentlichen aus folgenden Baugruppen

- 1. Spannungs-Strom-Wandler

- 2. Komparator

- 3. Band-gap-Referenzquelle

- 4. Ringoszillator

- 5. Teilerkette

- 6. Zähler mit-Zusatzlogik

- 7. Kontroll- und Steuerlogik

- 8. Multiplexer

- 9. . Digitalausgänge

## 5.1. Der Spannungs-Strom-Wandler

Die an den Eingängen pin 10 und 11 angelegte Spannung wird in dieser Stufe in einen Strom umgesetzt, mit dem der am pin 12 angeschlossene Integrationskondensator  $C_T$  in der 1. Phase der AD-Wandlung aufgeladen wird. Dieser Wandler besteht im wesentlichen aus einem Differenzverstärker mit einer Darlington-Eingangsstufe und vorgeschaltetem Substrat-Transistor zur Minimierung der Eingangsströme. Die Speisung des Differenzverstärkers erfolgt über eine Reihe von Stromquellen. An dem Differenzverstärker erfolgt der Nullpunktabgleich des Wandlers entsprechend einem Offsetabgleich eines OPVs über die pins 8 und 9. Durch zusätzlich eingespeiste Ströme in die beiden Zweige des Differenzverstärkers wird er eingangsseitig abgeglichen bzw. um einen gewünschten Betrag im Nullpunkt verschoben. Die beiden Eingänge des C 520 D sind durch interne Schutzmaßnahmen bis ± 15 V, bezogen auf Betriebsspannungsmasse pin 7 geschützt.

#### 5.2. Komparator

42

Der Ladezustand der Integrationskapazität wird mit dem Komparator ausgewertet. Er schaltet beim Erreichen seiner Schwellspannung, die etwa bei U<sub>S</sub> - U<sub>BE</sub> (4,3 V) liegt, um und startet bzw. stoppt über Schalttransistoren die Taktung der Zählkette, je nachdem welche Phase der AD-Wandlung abgearbeitet wird. Der Komparator gehört zum Analogteil des C 520 D. Seine Ausgangspegel betragen für low ≈ 50 mV, für high ≈ 660 mV und sind damit I<sup>2</sup>L-gerecht. Zwischen Komparator und Logikteil sind keine Anpaßstufen erforderlich.

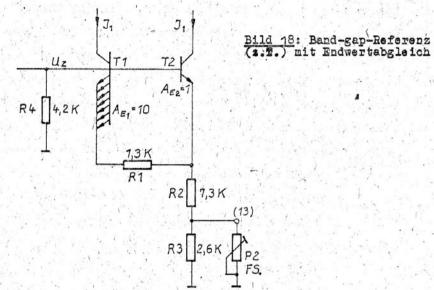

### 5.3. Band-gap-Referenzquelle

In der Bipolartechnik werden als Referenzelemente in zunehmendem Maße Band-gap-Quellen zur Bereitstellung von Referenzpegeln, wie z.B. im B 260 D, C 520 D eingesetzt. Für separate Spannungsreferenzen mit niederohmigem Ausgang finden sie ebenso Verwendung wie als Referenzspannung in programmierbaren oder Festspannungsreglern. Das Temperaturverhalten der Referenzspannung wird im wesentlichen durch das Emitterflächenverhältnis zweier Transistoren und durch das darauf angepaßte Verhältnis zweier Widerstände bestimmt. Theoretisch kann der TK der Referenzspannung durch die exakte Anpassung des Flächenverhältnisses der Transistoren und des Widerstandsverhältnisses zu Null gemacht werden. Bedingt durch technologische Unsicherheiten und Parameterschwankungen kann ohne Abgleich der Widerstände dieses angepaßte Verhältnis kaum erreicht werden. Es bleibt ein TK von bis zu 🕿 ± 100 ppm/°C für unabgeglichene Band-gap-Quellen. Besteht die Möglichkeit, Widerstände auf dem Chip abzugleichen, kann das Widerstandverhältnis auf das Flächenverhältnis angepaßt werden und der TK bis auf etwa 10 ppm/°C gesenkt werden. Eine Abgleichmöglichkeit besteht bei diffundierten Widerständen nur bedingt.

Im C 520 D wird mit einer unabgeglichenen Band-gap-Quelle ein Referenzstrom erzeugt, der in der zweiten Phase der Wandlung die aufgeladene Integrationskapazität entlädt, bis die Schwellspannung des Komparators erreicht wird. Mit dem am pin 13 angeschlossenen Endwertpotentiometer P 2 wird direkt das Widerstandsverhältnis der Band-gap-Referenz beeinflußt und damit auch die Höhe des Referenzstromes. 43 Dadurch kann die Wandlerkennlinie in ihrer Steilheit varliert und der Endwert (FS.) abgeglichen werden. Nachteilig daran ist, daß mit dem Potentiometer P 2 direkt in das den TK beeinflussende Widerstandsverhältnis eingegriffen wird. D.h., der Endwertabgleich des C 520 D beeinflußt auch dessen Temperaturverhalten. Im Bild 18 ist ausschnittsweise die Referenzquelle mit dem Abgleichpin 13 gezeigt.

Die temperaturstabile Spannung U<sub>z</sub> berechnet sich zu U<sub>z</sub>  $\approx$  1,21 V + (2 ·  $\frac{R_2 + R_3 \parallel P2}{R_1}$  ·  $\frac{k}{P2}$  ·  $\ln \frac{A_{E1}}{A_{E2}}$  · 0,002) ·  $\sqrt{\frac{P}{R_1}}$

k - Boltzmann-Konstante

q - Elementarladung

Der Term in der Klammer muß gegen O gehen, um in erster Näherung den Temperatureinfluß auf U, zu eleminieren,

Die restlichen Funktionseinheiten gehören zum Digital- und damit zum I<sup>2</sup>L-Teil des C 520 D, wenn man von den Ausgangstransistoren der Digitalausgänge absieht.

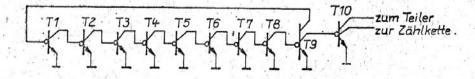

### 5.4. Oszillator

Er besteht aus einem 9-stufigen Ringoszillator, dessen Taktfrequenz stark vom Injektorstrom der I<sup>2</sup>I-Gatter und damit von den internen Verzögerungszeiten abhängt. Zwischen einzelnen Bauelementen sind Taktfrequenzschwankungen von 0,2 bis 1,3 MHz möglich. Da für den Oszillator aber nur Kurzzeitstabilität für Zeiten bis zu<sup>6</sup>5 ms zu fordern ist und der Absolutwert nur in die Wiederhelrate eingeht, erfüllt er alle Anforderungen. Alle anderen Takte werden aus der Oszillatorfrequenz abgeleitet, schwanken also ebenfalls in diesen weiten Grenzen. Den einfachen Aufbau des Oszillators zeigt Bild 19. T 10 dient zur Auskoppelung des Signals.

### Bild 19: 9-stufiger Ringoszillator

### 5.5. Teiler

Der Teiler ist aus T-Flip-Flops in I<sup>2</sup>L-Technik aufgebaut. Jedes T-Flip-Flop besteht aus sieben I<sup>2</sup>L-Gattern mit ein bis drei Kollektoren. Der gesamte Teiler besteht aus 19 Flip-Flops, die aus der Taktfrequenz des Oszillators, die direkt den Meßwertzähler ansteuert, zusätzlich die Takte für die Multiplexierung und die zeitliche Steuerung der Integrationszyklen bereitstellt. Nach 12 bzw. 13 Teilern erfolgt der Abgriff für den Multiplextekt und für die Steuertakte der Integrationszyklen in der schnellen Betriebsart.

In den restlichen Teilerstufen erfolgt die Untersetzung für die langsame Betriebsart mit zwei bis sieben Messungen/sec.. Gegenüber der schnellen Wiederholrate erfolgt für die Meßwertaufnahme und -umsetzung eine Teilung um den Faktor 24.

### 5.6. Zähler mit Zusatzlogik

Der Zähler ist als synchroner 3<sup>1</sup>/2 -Dekadenzähler ausgelegt. Er ist aus D-Flip-Flops aufgebaut. Sein maximaler Zählerstand beträgt "1999 ". Davon werden die letzten drei Dekaden zur Meßwerterfassung und die Tausenderstelle (MSD) zur Analyse des Vorzeichens herangezogen. Nach jeder Messung und Ausgabe wird der gesamte Zähler zurückgesetzt.

Die Aufintegrationsphase des Eingengssignals wird vom Zählerstand Null bis zur 880 festgelegt. Daraus ergibt sich eine Zeit t, von

880 Takte > t1 > 880 Takte 1,3 MHz 0,2 MHz

4,4 ms > t1 > 0,7 ms

Die nachfolgenden 20 Takte werden für Umschaltvorgänge verwendet.

Der negative Meßbereich von -1 mV bis -99 mV wird mit dem Zählerstand 901 bis 999 kodiert. Die 901 entspricht den -99 mV. Eine zusätzliche Negation und Komplementbildung, die vom Vorzeichen - der Tausendstelle - gesteuert wird, wird für den Zählerstand 901 bis 999 aktiviert und realisiert die Umkodierung. Mit dem Übergang von der 999 zur 1000 wird das negative Vorzeichen gelöscht, so daß die Umkodierung ausgeschaltet wird. Der positive Meßbereich wird durch den Zählerstand 1000 bis 1999 entsprechend OOO mV bis 999 mV ausgegeben. In der Zusatzlogik ist keine Unterdrückung der führenden Nullen enthalten. Mit dem Erreichen des Wertes 2000 wird ein Zusatz Flip-Flop gesetzt und die Ausgabe des positiven Überlaufs in allen drei Dekaden durch die Digitalkombination HIHH 2 11 angezeigt. Das negative Vorzeichen wird durch die Kombination HIHL 2810 im MSD, der Hunderterstelle, ausgegeben. Gewonnen wird das negative Vorzeichen aus der im Zähler in der dritten Dekade stehenden 9. Für Eingangsspannungen < -99 mV wird die 10 in allen drei Digits ausgegeben. Schaltungstechnisch wird die Sonderzeichenausgabe durch etwa 35 I<sup>2</sup>L-Gatter gelöst.

## 5.7. Kontroll- und Steuerlogik

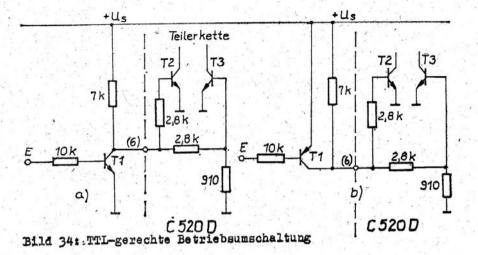

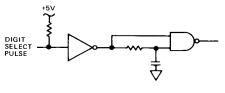

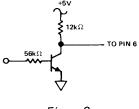

Die Logik realisiert die Bereitstellung von Steuersignalen je nach Zählerstand, die die Phasen der AD-Wandlung steuern, wie z.B. das Umschalten auf die Entladung durch den Referenzstrom. Weiterhin wird in dieser Baugruppe die Umschaltung der drei Betriebsarten gelöst. Im Bild 34 wird die TTL-gerechte Ansteuerung am Fin 6 und ein Teil der sich daran anschließenden Schaltung gezeigt. Die Transistoren T 2 und T 3 greifen mit

ihren Kollektoren direkt in die Teilerkette ein und schalten dert die Wiederholrate um bzw. den Wandler in den Holdbetrieb.  $U_6 = 0 \dots 0,4$  V: T 2 und T 3 sind gesperrt. Der Teilerkettenausgang des 18. Flip-Flops steuert die Wiederholrate des AD-Wandlers. Er führt zwei bis sieben Messungen/sec. aus.  $U_6 \ge 3,2$  V : T 2 und T 3 sind durchgesteuert. Der Takt für Lie Wiederholrate der Messung wird bereits nach dem 12. bzw. 13. Flip-Flop der Kette abgenommen. Er führt 48 bis 168 Messungen/sec. durch.

0.8 V  $\leq U_6 \leq 1.6$  V: T 2 ist offen und T 3 gesperrt. Dieser Zustami Slockiert die weitere Auslösung von Messungen. D.h., der letzte Meßwert bleibt im Zähler stehen und wird mit dem Multiplextakt, der von der Taktunterbrechung nicht berührt wird, ständig ausgegeben.

#### 5.8. Multiplexer

Für die Ausgabe des Zählerstandes wird ein Multiplexer verwendet, der nacheinander die drei BCD-Worte an die Ausgangsstufen legt. Der Multiplexbetrieb hat folgende Vorteile.

- Statt 3 x 4 = 12 Ausgänge werden nur 4 + 3 = 7

Ausgänge benötigt, so daß sich die Zahl der Anschlüsse reduziert.

- Der Leistungsverbrauch des Bauelementes sinkt und das Temperaturverhalten verbessert sich.

- Da die Anzeigen im Multiplexbetrieb angesteuert, werden, sinkt deren Stromverbrauch.

Es wird nur ein BCD- zu 7-Segment-Dekoder benötigt.

Die Schaltung erfordert dafür zusätzlich drei Digittreibertransistoren. Der Multiplexer verwendet die um den Fektor 2<sup>12</sup> und 2<sup>13</sup> heruntergeteilte Oszillatorfrequenz. Die Multiplexausgabe ist so ausgelegt, daß der Wandler im Betrieb mit der hohen Umsetzrate jeden Meßwert genau einmal zur Anzeige bringt. Durch die Untersetzung der Meßwertaufnahme im langsamen Betrieb ergibt sich, daß jeder umgewandelte Meßwert 24 Mal ausgegeben wird. Der Multiplexer besteht aus 9 I<sup>2</sup>I-Gattern mit 1 bis 4 Kollektoren.

Im Bild 30 ist das Taktdiagramm der Multiplexierung enthalten.

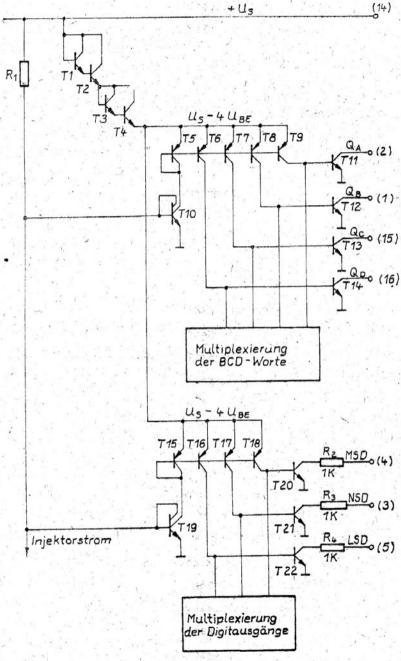

#### 5.9. Ausgangsstufen

Die Innenschaltung der digitalen Ausgänge zeigt Bild 20. Die BCD-Ausgänge sind reine open-Kollektor-Stufen. Die Digit-Ausgänge haben zur Strombegrenzung einen internen 1 kOhm-Schutzwiderstand. Die Transistoren gehören nicht zum I<sup>2</sup>L- Teil. Die Bereitstellung der internen Betriebsspannung erfolgt über T 1 bis T 4 ( $U_{\rm S}$  - 4 •  $U_{\rm RE}$ ). Die Ausgangstransistoren werden über die Strombänke T 6 und T 16 his T 18 versorgt. Die Führung der Strombänke wird über die Transistoren T 5/ T 10 bzw. T 15/ T 19 realisiert. Mit einem low-Signal am Ausgang der Multiplexierung werden die Ströme der Strombanktransistoren gegen Masse abgeleitet, so daß die Ausgangstransistoren gesperrt werden ( U<sub>CEsat</sub> < U<sub>BE</sub> ). Bei gesperrten Ausgangstransistoren der Multiplexierung werden die Steuerströme der Strombänke von den Ausgangstransistoren übernommen, die dann durchgesteuert werden ( Ausgang = low). Die BCD-Ausgangstransistoren werden bei  $I_{OL} = 1,6$  mA ( 1 TTL-Last) auf die Einhaltung von U<sub>OL</sub> = 0,4 V gemessen. Für die BCD- und Multiplexausgänge werden gleiche Ausgangsstrukturen verwendet.

Bild 20: Schaltung der Digitalausgänge

1 July 1 244

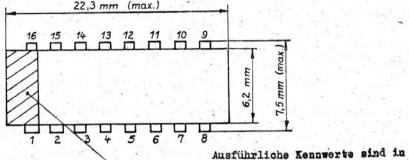

#### 6. KENNWERTE des C 520 D

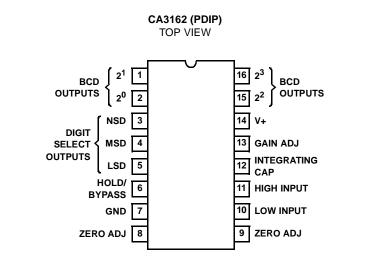

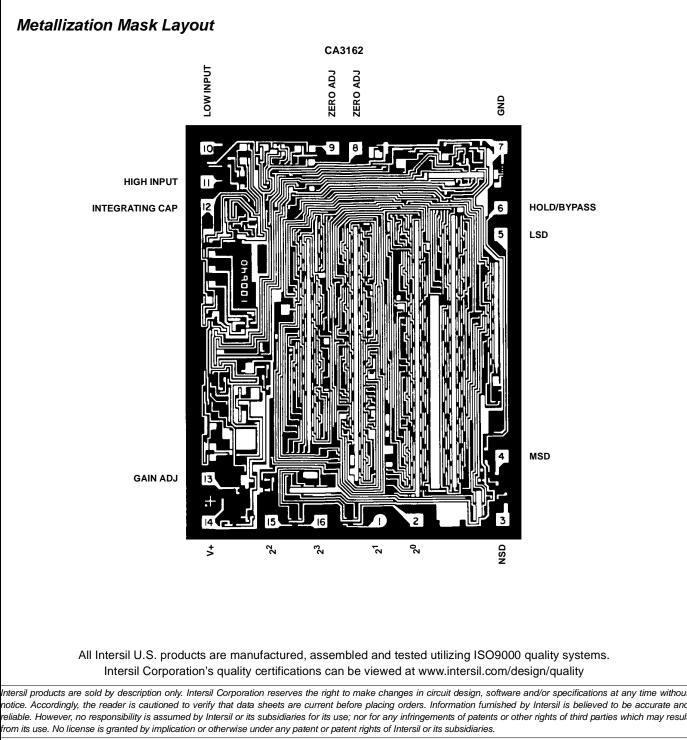

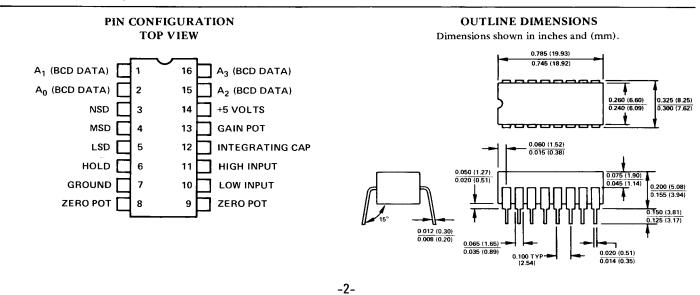

Bild 21 zeigt die Anschlußbelegung des 16-poligen DIL-Ge-

häuses und Tabelle 3 die dazugehörige Erläuterung.

Raum für Markierung /11/ und /12/ enthalten.

#### 6.1. Anschlußbelegung

Anschluß 1 BCD-Datenausgang Qn 2 BCD-Datenausgang QA NSD-Digitausgang (mittleres Digit) 3 MSD-Digitausgang (höchstwertiges Digit) 4 5 LSD-Digitausgang (letztes Digit) Hold-Geschwindigkeitsumschaltung 6 7 Masse Nullpunktabgleich 8

9 Nullpunktabgleich

10 Eingang "low "

11 Eingang "high "

12 Integrationskondensator

- 13 Endwertabgleich

- 14 Betriebsspannung U.

- 15 BCD-Datenausgang Q

- 16 BCD-Datenausgang QD

Tabelle 3: Anschlußbelegung des C 520 D

51

Gehäuse : 15-poliges DIL-Plastgehäuse oder Bauform 21.1.1.2.16 Rach IGL 26 713.

## 6.2. Grenzwerte

Grenzwerte, die im Betrieb nicht unter- bzw. überschritten werden dürfen weist folgende Tabelle aus.

| Kenngröße        | Kurz-<br>zeichen | Einheit  | Kleinst-<br>wert                      | Größtwert |

|------------------|------------------|----------|---------------------------------------|-----------|

| Betriebsspannung | U,               | V        | 0                                     | 7         |

| Spannung an      |                  |          |                                       |           |

| Eingang "high"   | <sup>U</sup> 11  | V        | -15                                   | +15       |

| und " low "      | <sup>U</sup> 10  | V        | -15                                   | +15       |

| Spannung an den  |                  |          |                                       |           |

| BCD-Kode-und     | Ug               | V        | . 0                                   | 7         |

| Digit-Ausgängen  |                  |          |                                       |           |

| Spannung für Be- | 1. Carl          |          |                                       |           |

| triebsartenum-   | U6               | <b>v</b> | • <b>0</b> • • •                      | 7         |

| schaltung        |                  |          | · · · · · · · · · · · · · · · · · · · |           |

Alle Spannungen sind auf Masse (pin 7 ) bezogen.

Tabelle 4 : Grenzwerte des C 520 D

| Kenngröße                                                   | Symbol             | Einheit        | Kleinst-<br>wert         | Größtwert |

|-------------------------------------------------------------|--------------------|----------------|--------------------------|-----------|

| Betriebsspannung                                            | U <sub>s</sub>     | V              | 4,5                      | 5,5       |

| Umgebungstemperatur                                         | v <sub>a</sub>     | ٥ <sup>0</sup> | 0                        | 70        |

| Eingangsspannung<br>zwischen den An-<br>schlüssen 10 und 11 | <sup>U</sup> 10/11 | v              | -0,099                   | 0,999     |

| Spannung für Ge-<br>schwindigkeitsum-                       |                    |                | ν.<br>1 <sup>4</sup> - Γ |           |

| schaltung                                                   | υ6                 |                |                          |           |

| Normal-Betrieb                                              |                    | V              | 0                        | 0,4       |

| Hold-Betrieb                                                |                    | v              | 0,8                      | 1,6       |

| High-speed-Betrieb                                          |                    | v. <b>v</b>    | 3,2                      | 5,5       |

Tabelle 5 : Betriebsbedingungen des C 520 D Abgleichbedingungen: Nullpunktabgleich bei U<sub>i</sub> = 0 mV Endwertabgleich bei U<sub>i</sub> = 900 mV

| Elektrische Kennwerte für Va = 25°C -5 K:                 | für Va | = 25°0 -         |                                                                                                                                         |                            | •                   |                                          |

|-----------------------------------------------------------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|------------------------------------------|

| Rønngröße                                                 | Symbol | Einheit          | Symbol Einheit Meßbedingungen                                                                                                           | Kleinst- Typ-<br>wert wart |                     | Größt-<br>wert                           |

| Stromaufnahme                                             | IS     | ЧШ               | $U_{14} = 5.0 V$<br>$U_6 = 1.2 V$                                                                                                       |                            | 10,0                | 17                                       |

| Fehler der<br>Linearität                                  | FLin   | % vom<br>Meßwert | U <sub>14</sub> ≥5,0 V;U <sub>6</sub> <b>≤</b> 0,4V<br>U <sub>10</sub> ≥ 0 V<br>-99 <u>m</u> W€ U <sub>11</sub> € 999 <u>m</u> V        | -0,1-1Digi                 | t ± 0,05<br>± 1046t | -0,1-1Digit ± 0,05 0,1+1Digit<br>± 1Digt |

| T-dusganga-<br>spannung der<br>BÖD-Kode-Aus-<br>gänge     | TOn    | ٨щ               | $U_{14} = 5,0V; I_{0L} = 1,6 mA$<br>$U_6 = 1,2 V$<br>$U_{10} = U_{11} = 0V$                                                             |                            | 8                   | 004                                      |

| Gleichtekt-<br>unterdrückung                              | CMR    | θġ               | $u_{14^{\pm}} 5, 0V; U_{6} 0, 4 V$<br>$u_{10} = u_{11} = U_{CM}$<br>-200 mV $\neq U_{CM} \neq 200$ mV                                   |                            | 47                  |                                          |

| Betriebs- Nullpunkt<br>Spannungs Endwert<br>unterdrückung | RVS    | g                | $\mu_{15} \neq U_{\eta_{11}} \neq 5.5 V U_{\eta_{1}} = 0 V(MP)$<br>$U_{6} \neq 0.4 V_{1} U_{\eta_{0}} = 0 V U_{\eta_{1}} = 900 mV (BW)$ |                            | 25                  |                                          |

| Stromaufn. der<br>RCD-Kode-Aussänge                       | IOL    | - War            | $U_{0L} = 400mV; \hat{U}_{14} = 5,0 V$                                                                                                  | 1,6                        | 5.1                 |                                          |

| Stromaufuahme der<br>Digit-Ausgänge                       | PI     | mA               | $u_0 = 4 v$                                                                                                                             | 1,6                        | 3,6                 |                                          |

| Reststromaufnahme der 10S                                 | Tos    | ph               | $u_{14} = 5,0 \text{ V}; u_6 = 1,2 \text{ V}$<br>$u_{10} = u_{14} = 0 \text{ V}$                                                        |                            | 500                 |                                          |

Elektrische Kennwerte 6.4.

| Kenngröße                                 | Symbol.        | Symbol   Einheit | Me Bbedingungen                                                                                    | Kleinst- | Typ-<br>wert | Größt-<br>wert | 1 - P |

|-------------------------------------------|----------------|------------------|----------------------------------------------------------------------------------------------------|----------|--------------|----------------|-------|

| Reststromaufnahme<br>der Digit-Ausgänge   | Los            | ЪÅ               | $U_{14} = 5 V$ $U_6 = 1_9 2 V$                                                                     |          | 500          |                | 1     |

| Bingangas trom<br>Bingang 'high           | ۲h             | рА               | Nullpunktabgleich mit<br>50 kOhm-Regler<br>U <sub>14</sub> = 5 V                                   |          | 124          |                |       |

| m des Null-<br>punktes                    | TRKND          | Juv/E            | $U_{10} = U_{11} = 0 V$<br>$U_6 \le 0.4 V$<br>$0 \le J_{a} = 70^{0}C$<br>$U_{14} = 5 V$            |          | 28           |                |       |

| IK des<br>Endwertes                       | IIK            | PPm/K            | $U_{11} = 900 = V; U_{10} = 0 V$<br>$0 \le 9_a \le 70^{\circ}c; U_{e} \le 0,4 V$<br>$U_{14} = 5 V$ |          | 27           |                | 1.1   |

| Wandlungsrate für<br>normale Betriebsart  | Ums . s        | ۲                | U <sub>6</sub> ≰0,4 V<br>U <sub>14</sub> = 5 V                                                     | α,       | 5            | 7              | 10    |

| Wandlungsrate für<br>schnelle Betriebsart | Ums . B-1      | ٢                | U <sub>14</sub> = 5 V<br>3,2 V ≤ U <sub>6</sub> € 5,5 V                                            | 48       | 122          | 168            | ÷ .   |

| Für Betriebsart Hold<br>notw. Spennung    | n <sub>6</sub> | >                | $u_{14} = 5 V$                                                                                     | 0,8      |              | 1,6            |       |

|                                           |                |                  |                                                                                                    |          |              | 1              |       |

Tabelle 6 : Elektrische Kennwerte des C 520 D

### 6.5. Sonderzeichenausgabe

Da das Bauelement über eine automätische Polaritäts- und Uberlauferkennung verfügt, sind für diese Zustände Sonderzeichen über die BCD-Ausgänge nach außen zu geben. In Tabelle 7 sind sie zusammengestellt und ihre Dekodierung durch den D 147 C im 7-Segment-Kode angegeben.

| Funktion                             | Sonderzeichen           | Dekodierung D 147 C |

|--------------------------------------|-------------------------|---------------------|

| positives Vorzeichen                 | keine Kennzeichnung     | 888                 |

| negatives Vorzeichen                 | HIHI 10 im MSD          | = <u>198</u>        |

| positive Bereichs-<br>überschreitung | HLHH = 11) in<br>(allen | בבב                 |

| negative Bereichs-                   | drei                    |                     |

| überschreitung                       | HLHL = 10 Digits        | EEC                 |

Tabelle 7 : Sonderzeichenausgabe

56

Neben den in den Tabellen enthaltenen Daten sind beim Einsatz des Wandlers einige Besonderheiten zu berücksichtigen. Die Meßeingänge des C 520 D sind keine echten Differenzeingänge. Die Komponenten Betriebsspannung, Eingangsspannung, maximaler Hub über dem Integrationskondensator und maximale Gleichtekteingangsspannung sind in Grenzen gegeneinender, bezogen auf die zu lösende Aufgabe, abzuwägen. Es kann unter Umständen sinnvoll sein, die Betriebsspannung an die obere zulässige Grenze zu legen, den Hub über dem Integrationskondensator bis an die Grenze der geforderten Linearität und Auflösung zu verkleinern, um einen maximalen Gleichtektbereich für den Wandler zu realisieren. Mit der verhältnismäßig kleinen Betriebsspannung von  $U_{\rm S}$  = + 4,5 ... + 5,5 V ist der maximal zulässige Gleichtaktbereich auf  $U_{\rm CM}$  = ± 200 mV beschränkt.

Die Bauelemente verarbeiten in der Regel Gleichtaktspannungen bis  $U_{CM} = \pm 280$  mV bei  $U_S = \pm 5$  V ohne erkennbare zusätzliche Linearitätsfehler, wenn der Wandler sowohl im Nullpunkt als auch im Endwert neu abgeglichen wird.

Nutzt man bewußt die Gleichtaktgrenzen des C 520 D, so ist zu beachten, daß die Linearität dann zwangsläufig an den Eingangsspannungsgrenzen verloren geht.

Für die Temperaturmessung werden diese Grenzen unter Umständen gar nicht erreicht. Die typische Gleichtaktunterdrückung beträgt bei  $U_i = 0$  mV (Eingangskurzschluß) etwa CMR (Typ) = 47 dB und etwa CMR (Typ) = 42 dB für Eingangssignale von  $U_i = 900$  mV. D.h., sich bis an die zulässigen Grenzen ändernde  $U_{CM}$  führen zu Meßfehlern, während konstante Gleichtakteingangsspannungen in den zulässigen Grenzen durch einen Abgleich des Wandlers keine erhöhten Meßfehler verursachen.

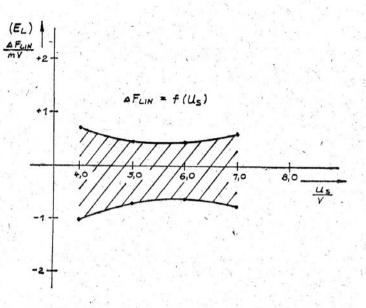

Der Wandler weist eine ausgezeichnete Betriebsspannungsunterdrückung auf. Der typische Wert wurde mit 75 dB für den Nullpunkt und mit SVR = 69 dB für U<sub>i</sub> = 900 mV ermittelt. Von wesentlichem Interesse für den Einsatz des Wandlers ist der Betriebsspannungsbereich, in dem er funktionstüchtig ist. Getestet wurde die Funktion mit der Einsatzschaltung nach Bild 27. Die Wandler sind im Bereich (3,8 V) 4,0 V - U<sub>S</sub> - 7 V funktionstüchtig. Bis zu diesen Grenzen verschlechtert sich die Linearität gegenüber den Fehlern bei U<sub>S</sub> = +5 V kaum, wie Bild 22 zeigt.

### Bild 22: Linearität in Abhängigkeit von Us

Durch die hohe Betriebsspannungsunterdrückung ist ein Neuabgleich bei sich ändernder Betriebsspannung bei fast keinem Bauelement erforderlich.

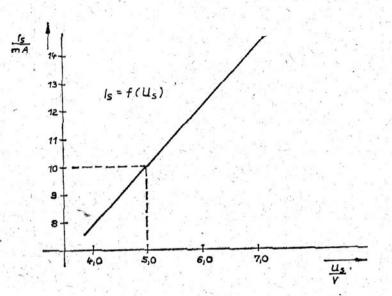

Die Stromaufnahme bei  $U_s = 5$  V liegt bei typisch  $I_s = 10$  mA. Die Verlustleistung beträgt damit  $P_v = 50$  mW. Verglichen mit der Stromaufnahme des D 147 C und der LED-Anzeigen ist sie sehr gering.

Bild 23: Stromaufnahme in Abhängigkeit von Us

Im Abschnitt 9. wird ein Ausblick auf eine stromarme B**60-** zu 7-Segment-Dekoderreihe gegeben.

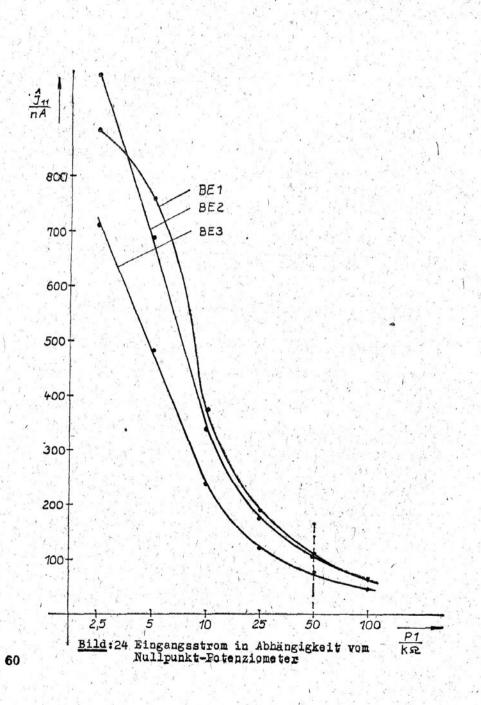

Der Eingengsstrom des Wendlers fließt nur, wenn der U/I-Wandler an des Meßsystem geschaltet ist und das Eingengssignel aufintegriert wird. Die Integrationszeit beträgt 0,7 bis 4,4 ms ( typ. 1 ms ). Während dieser Zeit fließt der Eingengsstrom von typisch 120 nA, bei einer Beschaltung des Nullpunktabgleiches mit einem 50 kOhm - Potentiometer. Der Widerstand zwischen den Anschlüssen 8 und 9 beeinflußt den Eingengsstrom. Je niederohmiger  $R_1 + R_2 + P_1$  gewählt wird, desto größer wird der Eingengsstrom. Die Abhängigkeit für drei Bauelemente zeigt Bild 24.

Größer als 100 kOhm sollte die Summe nicht gewählt werden, da dann die Linearität negativ beeinflußt wird. Wie auch aus dem Bild zu ersehen ist, kann  $I_{11} = I_i$  erheblich von Bauelement zu Bauelement schwanken. Als obere Grenze bei einer Beschaltung mit 50 kOhm kann mit 180 ... 200 nA gerechnat werden.

Wahrend der Meßwertausgabe ist der U/I-Wandler abgeschaltet. Dann fließt ein Reststrom von **<** 100 pA. Die Messung und Anzeige seines eigenen Eingangsstromes kann vom Wandler vorgenommen werden. Schaltet man zwischen die Eingänge 10 und 11 einen 1 MOhm - Widerstand (ohne Eingangssignal) ergibt die Anzeige mit 1 mV Auflösung eine Anzeige des Eingangsstromes in nA.

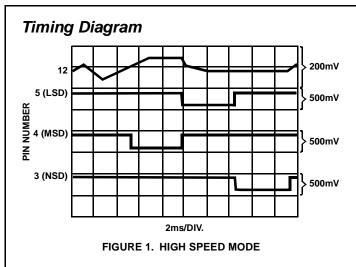

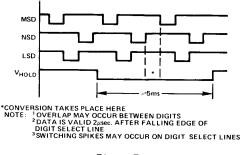

Zu beachten ist weiterhin, daß wie aus Bild 30 zu ersehen ist, die Meßwertausgabe nicht reihenfolgerichtig erfolgt. Nach der Umsetzung wird erst das MSD ( $10^2$ ), dann das LSD ( $10^0$ ) und danach das NSD ( $10^1$ ) ausgegeben.

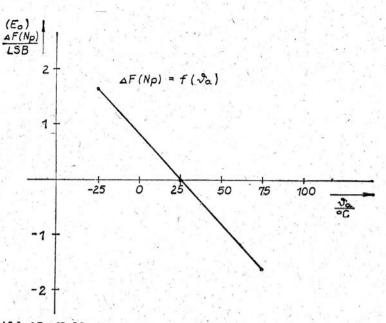

### 6.6. Temperaturverhalten

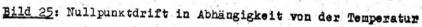

Neben dem zulässigen Umgebungstemperaturbereich von O bis 70°C sind Nullpunkt- und Endwertdrift in Abhängigkeit von der Temperatur entscheidend. Die Bilder 25 und 26 zeigen das Verhalten des Wandlers.

TK (Np) ≈ 28 /uV/K im Bereich von 0 bis 70°C

TK (EW)  $\approx 27 \text{ ppm/}^{\circ}$ C bei U<sub>i</sub> = 900 mV im Bereich von O bis 70°C.

Da bei der Endwertdrift die Nullpunktverschiebung enthalten ist, handelt es sich bei Temperaturänderungen fast nur um eine Parallelverschiebung der Kennlinien. Die Differenz zwischen diesen beiden Werten ergibt die Steilheitänderung der Kennlinie, die sehr gering ist. Zu beachten ist z.B., daß beim Einsatz in Handmeßtechnik, bei der die Betriebsspannung nur kurzzeitig zur Messung eingeschaltet wird, das Bauelement erst nach > 20 sec. ( 30 sec.) temperaturmäßig eingelaufen ist, d.h., die stabile Chiptemperatur erreicht wird. Wird der Wandler nicht im abgeglichenen Zustand betrieben, kann sich der Temperaturverhalten des C 520 D verändern. Daraus folgt nicht unbedingt, daß es sich verschlechtert. Bedingt durch technologische Schwankungen kann das Temperaturverhalten durch einen Fehlabgleich unter Umständen auch verbessert werden.

## 7. APPLIKATIVE HINWEISE zum EINSATZ. des C 520 D

- Die Betriebsspannung ist mit einem Elektrolytkondensator

≥ 50 /uF und einem Scheibenkondensator

≥ 47 nF nahe am

Schaltkreis gegen Masse abzublocken.

- Bei der Betriebsspannungs- und Masseführung ist darauf zu achten, daß die niederfrequenten Schaltvorgänge des Anzeigeteils nicht die Analogeingänge des Wandlers beeinflussen. Es dürfen keine Ströme des Digitalteils über die Analogmasse fließen.

- 3. Da der C 520 D wegen der kurzen Integrationszeit des Eingangssignals keine Brunmspannungsunterdrückung aufweist, sollte im Bedarfsfall ein Tiefpaßfilter für den high - Eingang (11) vorgesehen werden.

- Zur Erhöhung der Abgleichgenauigkeit sind als Abgleichpunkte folgende definierte Eingengsspennungen zu wählen

U<sub>i</sub> = 0,5 mV, die Anzeige schwankt zwischen 000 und 001 und

U<sub>i</sub> = 900,5 mV, die Anzeige schwankt zwischen 900 und 901.

- 5. Als Integrationskapazität ist ein verlustarmer Wickelkondensator und für den Einsatz innerhalb eines größeren Temperaturbereiches mit möglichst geringem TK zu verwenden, da Kapazitätsänderungen einen zusätzlichen Linearitätsfehler verursachen können.

- 6. Für den Abgleich des Wandlers im Nullpunkt und Endwert sollten Dickschichtregler mit Spindelantrieb verwendet werden, da der Abgleichbereich in beiden Fällen sehr groß ist. Eine Eingrenzung durch zusätzliche Festwiderstände ist sinnvoll.

- Die Summe der Widerstände zwischen Anschluß 8 und 9 sollte 50 kOhm betragen. Kleinere Widerstände vergrößern den Eingangsstrom des Wandlers.

- Die BCD-Ausgänge sind open-Kollektorstufen. Zur Einhaltung der Schaltpegel für den D 147 C sind Widerstände ( 10 ... 20 kOhm ) gegen +U<sub>s</sub> vorzusehen.

- Die Multiplexausgänge sind open-Kollektorstufen mit internem 1 kOhm-Schutzwiderstand, so daß diese Ausgänge nicht TTL-kompatibel sind.

- 10. Bein Einsatz des C 520 D in meßwerterfassenden Systemen sind Schutzmaßnahmen für eine sichere Datenzwischenspeicherung vorzusehen, da in den drei Multiplexsignalen Störnadeln (HIR) enthalten sind. Mit Verzögerungsgliedern sind Störnedeln bis zu einer Breite von etwa t = 3/us zu beseitigen. In meßwertenzeigenden Systemen sind diese Schutzmeßnehmen nicht erforderlich.

- 11. Für meßwertanzeigende Systeme ist die langsame Betriebsart zu wählen, da Meßwertänderungen vom Auge besser verfolgt werden können.

### 8. ANWENDUNGSBEISPIELE für den C520 D

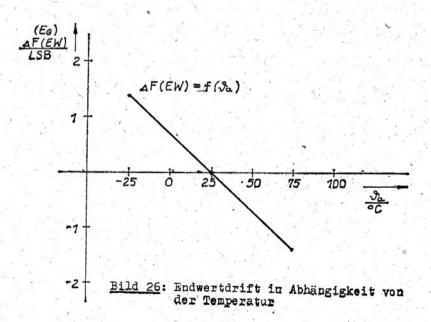

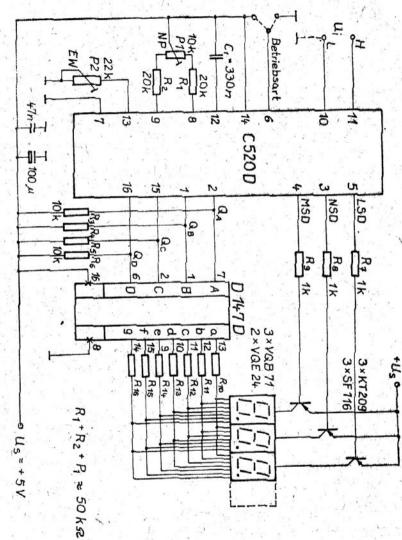

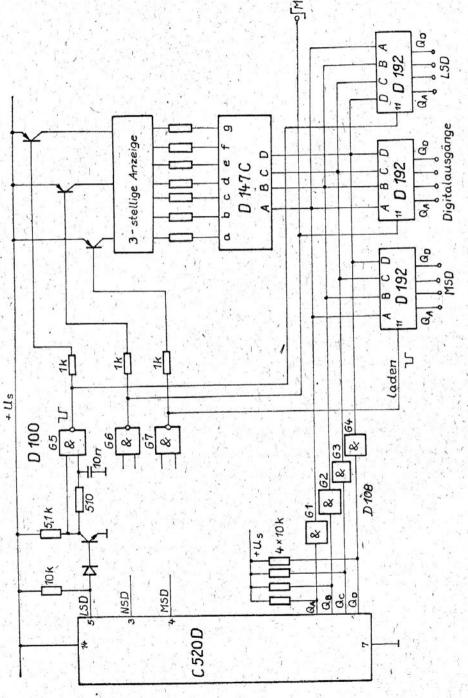

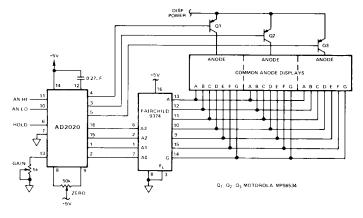

#### 8.1. Anzeigesysteme

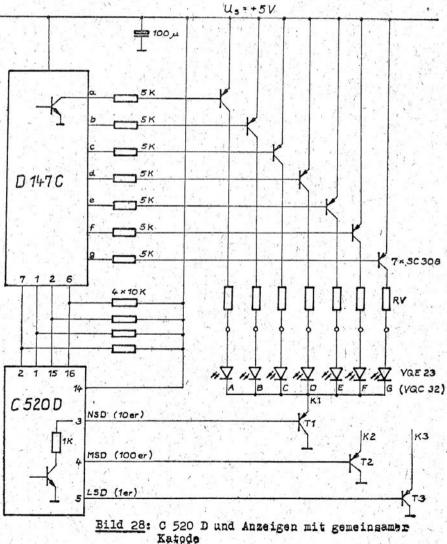

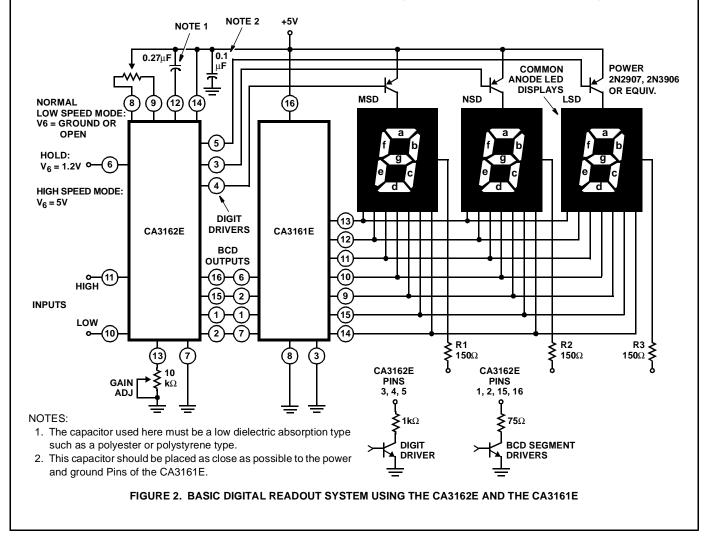

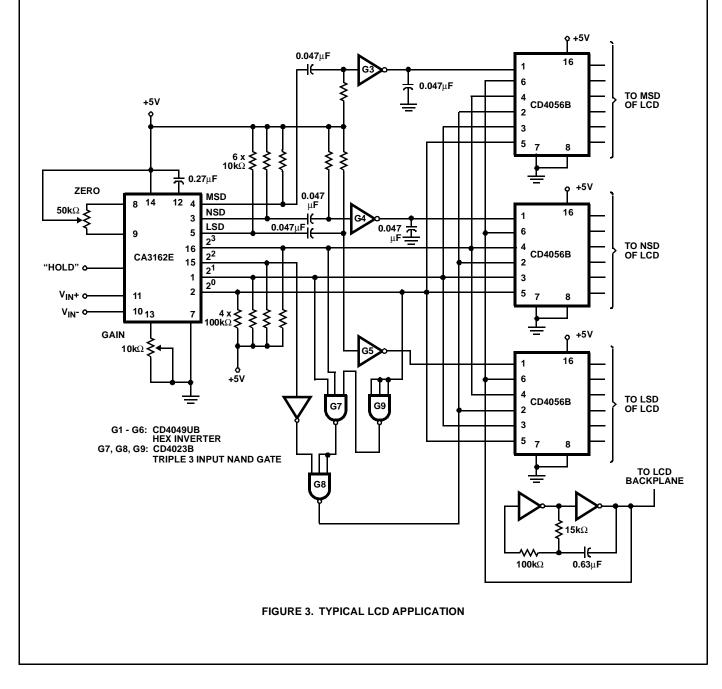

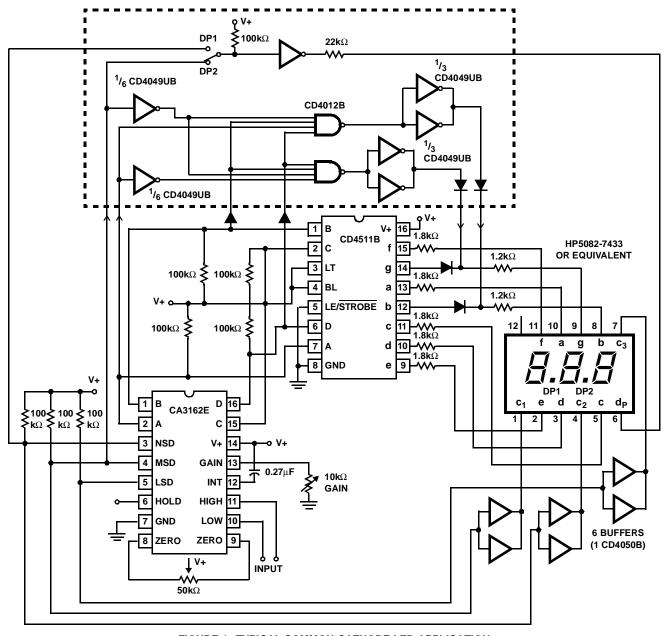

Im Bild 27 wird die Standardschaltung für Anzeigen mit gemeinsamer Anode gezeigt. In dieser Zusammenstellung ist eine minimale Bauelementezahl für den Aufbau erforderlich. Die Widerstände R2 bis R6 garantieren die TTL-gerechten Eingangspegel für den D 147 C. Ohne diese Widerstände stellt sich bei gesperrten Ausgangstransistoren ein Pegel im verbotenen Bereich ein, den der Dekoder aber als high erkennt. Ry bis Rg sind zur zusätzlichen Strombegrenzung für die Digitausgänge vorgesehen. Sie können entfallen, wenn die pnp-Treibertransistoren mit hohèm Basisstrom zu betreiben sind, um bei schlechtem B der Transistoren die geforderten Anzeigeströme zu schalten. Die Segmentströme sind durch die Aufnahmefähigkeit des D 147 C begrenzt. ( N<sub>OL</sub> (max.) = 12 3 I<sub>OL</sub> = 20 mA). Damit ergibt sich ein maximal zulässiger Anzeigestrom von 140 mA ohne Dezimalpunkt. Mit R10 bis R16 werden die Segmentströme festgelegt. Als Digittreiber sind für kleinere Ströme z.B. KT 209 und für höhere SF 116 bis 119 geeignet. In diesem Zusammenhang sei auf die im Abschnitt 9 vorgestellte neue Dekoderreihe des VEB HFO verwiesen. bei denen im Multiplexbetrieb bis zu Iot = 30 mA/ Segment zugelassen sind. Als Anzeigen kommen VQB 71 oder VQE 24 in Frage, wobei die eine nicht benötigte Ziffer der VQE 24 als Sonderzeichen wie z.B. als C (Grad) verwendet werden kann.

Für Anzeigesysteme ist die langsame Betriebsart zu empfehlen, da Meßwertänderungen besser verfolgt werden können. Im Bild 28 und 29 werden zwei Ansteuermöglichkeiten für Anzeigen mit gemeinsamer Katode gezeigt.

Dafür werden zusätzlich 7 pnp-Transistoren für die Segmentansteuerung benötigt, deren Basisstrom mit den 7 x 5 kOhm begrenzt wird. Als Anzeigen kommen VQC 32 oder VQE 23 in Frage. Als Digittreiber werden im Bild 28 pnp-Transistoren  $T_{1/2/3}$  eingesetzt. Das Katodenpotential  $K_{1/2/3}$  ergibt sich aus der Summe von  $U_{CE}$  +  $U_{BE}$  +  $T_B$  • 1 kOhm und kann damit je nach B der Transistoren  $T_1$  bis  $T_3$  schwanken und zu Helligkeitsunterschieden zwischen den drei Anzeigen führen. Bild 29 zeigt die Ansteuerung mit 2 npn-Transistoren, bei der das gemeinsame: Katodenpotential nur  $U_{CE}$  über der Masse liegt und keine B-Abhängigkeit aufweist.

# Bild 29: Ansteuerung von Anzeigen mit gemeinsamer Katode über ppn-Transistoren

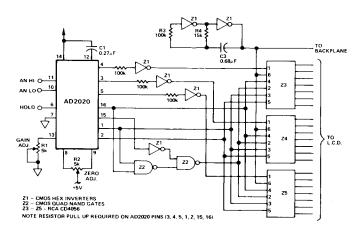

#### 8.2. Multiplexsignale

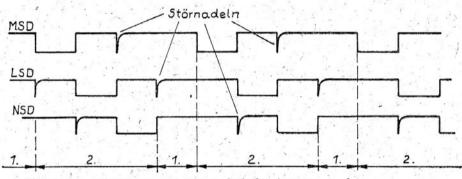

Im Bild 30 ist das Taktdiagramm der Multiplexierung enthalten. Bedingt durch das Schaltverhalten des Multiplexers treten in den Multiplexsignalen Spikes (HIH) auf. Die Leuchtzeit pro Digit beträgt etwa 2,3 ms. Die Umsetzzeit ist etwa ebenso lang, so daß sich für die Anzeigen ein Tastverhältnis von 4 : 1 ergibt.

Bild 30: Taktdiagramm der Multiplexierung

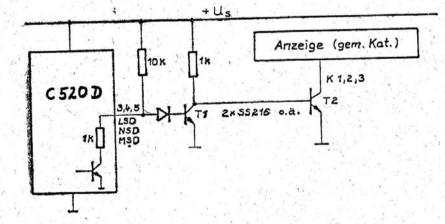

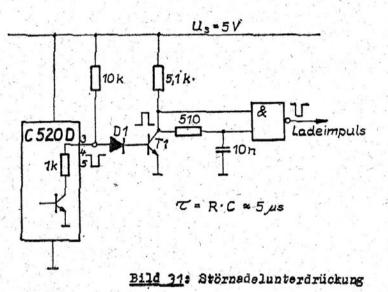

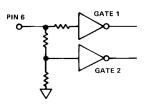

Die Störnadeln spielen bei Meßwertanzeigen keine Rolle. Für Meßwertspeicherungen sind sie zu unterdrücken, da ansonsten Fehlspeicherungen auftreten. Die Darstellung und Messung der Breite der Spikes ist schwierig, da die Wiederholrate nur bei 100 Hz liegt und die Nadeln max. 2 /us breit sind. Für die Unterdrückung wird ein R-C-Glied mit  $\mathcal{C} = 5$  /us verwendet. Bild 31 zeigt eine Schaltung zur Störnadelunterdrückung und Bereitstellung von TTL-Pegeln, da die Multiplexausgänge des C 520 D nicht TTL-kompatibel sind.

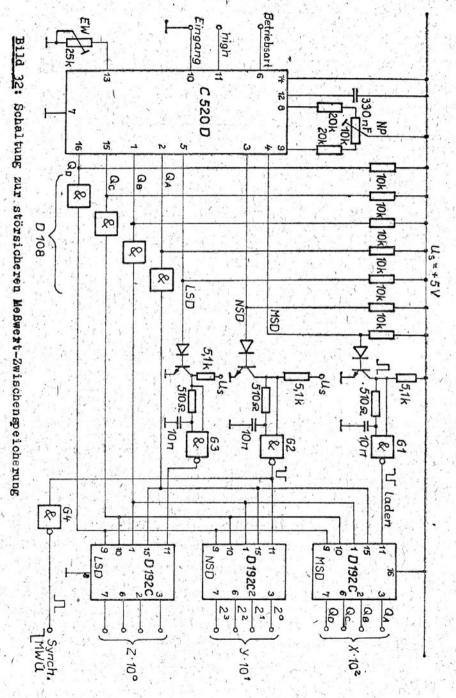

#### 8.3. Meßwertspeicherung

Zur Erhöhung des Schaltpegels von T<sub>1</sub> wurde D<sub>1</sub> eingefügt. Mit der RC-Kombination 510 Ohm und 10 nF wird für die Vorderflanke eine Verzögerung realisiert, die die Spikes unterdrückt. Mit dem Ladeimpuls nach dem Gatter kann die Zwischenspeicherung in D 192 O oder D 195 O erfolgen. Eine Schaltung zur Zwischenspeicherung in D 192/193 wird in Bild 32 gezeigt. Die Störnadelunterdrückung entspricht der vom Bild 31. Mit dem Low-Zustand der Gatter werden die dazugehörigen D 192/ 193 über pin 11 geladen. Die vier UND-Gatter des D 108 D entlasten die BCD-Ausgänge des C 520 D, da die drei TTL-Eingänge der D 192 C parallelgeschaltet sind.

Eild 23: MeBweranzeige und Speicherung

⊸โพพน้

Wie aus dem Taktdiagramm der Multiplexierung hervorgeht, wird das NSD ( $10^1$ ) als letztes ausgegeben. Das zusätzliche Gatter G<sub>4</sub> stellt einen Synchronausgang dar, mit dessen H/L-Flanke eine Meßwertübernahme in externe Systeme möglich ist. Wird statt der D 192/193 ein D 195 zur Speicherung verwendet, so sind die Ausgänge der Gatter G<sub>1</sub> bis G<sub>3</sub> auf die Takteingänge T<sub>2</sub> der D 195 zu geben und MC ist auf high zu legen. Ansonsten sind die Schaltungen identisch.

Soll gleichzeitig eine Meßwertanzeige und Zwischenspeicherung erfolgen, so wird die Multiplexierung der Anzeige wegen der Leistungsbilanz beibehalten.

Das Laden der Zwischenspeicher bleibt wie im Bild 31. Die Gatter G<sub>1</sub> bis G<sub>4</sub> entlasten die Ausgänge des C 520 D, da die vier Dateneingänge der D 192 und des D 147 C parallelgeschaltet sind. Die Meßwertübernahme (MWU) kann mit der L/H-Flanke des NSD-Multiplexsignals erfolgen.

#### 8.4. Betriebsartenumschaltung

Im Bild 34 ist eine TTL-kompatible Betriebsartenumschaltung dargestellt. Die Transistoren  $T_2$  und  $T_3$  des C 520 D greifen direkt in die Teilerkette ein und steuern die Zahl der Messungen/sec. Es ergeben sich folgende Umschaltmöglichkeiten für die beiden Ansteuerungen nach a) und b)

| a) | E    | υ <sub>σ</sub> ε | Geschwin-<br>digkeit | ъ)      | E | 0      | Geschwin-<br>digkeit |

|----|------|------------------|----------------------|---------|---|--------|----------------------|

|    | Ħ    | 40,4 V           | langsam              |         | H | 21,2 V | hold                 |

|    | T    | \$1,2 V          | hold                 | n de la | L | Us-UCE | l schnell<br>sat     |

|    | offe | n≈1,2V           | hold                 | C       |   | ≈1,2 V |                      |

Tabelle 8 : Geschwindigkeitsumschaltung nach Bild 34

Die Anwendung ist z.B. für die Speicherung von Maxima oder Minima von Interesse

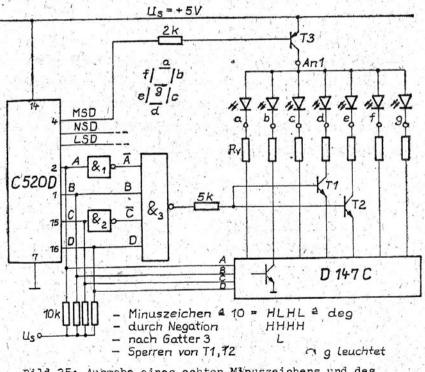

#### 8.5. Vorzeichenausgabe

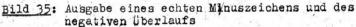

Die Unterscheidung des positiven und negativen Überlaufs kann leicht zu Verwechselungen führen. Im Bild 35 ist eine Möglichkeit gezeigt, wie das negative Vorzeichen und der negative Überlauf nur durch das Leuchten des Segments g der Anzeigen besser zu erfassen sind.

An den BCD-Ausgängen wird durch die Gatter  $G_1$  bis  $G_3$  eine 10-Erkennung realisiert.  $G_3$  geht am Ausgang auf low und sperrt die Transistoren  $T_1$  und  $T_2$  in den Segmentleitungen d und e. Der positive Überlauf wird davon nicht berührt.

Wird die Unterscheidung zwischen positivem und negativem Uberlauf nicht benötigt, können  $G_1$  und  $G_2$  entfallen. An  $G_3$ werden nur B und D angeschlossen. Der Ausgang von  $G_3$  geht dann bei 10 und 11 am Eingang auf low. Fügt man zu  $T_1$  und  $T_2$  noch  $T_3$  in der Segmentleitung c ein, dann werden die Segmente c, d und e bei 10 und 11 gesperrt. Es leuchtet in beiden Fällen nur das Segment g.

#### 8.6. Ergänzende Baugruppen

Für einige Einsatzfälle reicht die Empfindlichkeit des C 520 D mit 1 mV sicher nicht aus. Mit dem Bi-Fet-OPV B 081 D oder dem MAA 741 ist im Bild 36 ein Vorsatz-OPV gezeichent, der in Elektrometerschaltung arbeitet und damit einen besonders hohen Eingangswiderstand aufweist.

#### Bild 36: Hochohmiger OPV-Vorsatz

Mit  $R_1 = 10$  kOhm,  $R_2 = 90$  kOhm und  $R_3 = 9$  kOhm wird ein  $V_u = 10$  realisiert, so daß zusammen mit dem C 520 D eine Auflösung von 0,1 mV erreicht wird.

Die Dioden  $D_1$  und  $D_2$  stellen eine Schutzschaltung gegen positive und negative Überspannungen dar. Die Einstellung von  $V_u = 10$  erfordert keine übermäßige Genauigkeit, da der C 520 D sowohl den Nullpunkt- als auch den Verstärkungsfehler korrigieren kann. Beim Austausch des B 081 D gegen den MAA 741, die pinkompatibel sind, ist die niederohmigere Offsetkompensation des MAA 741 zu beachten. Die Funktion beider OPVs ist auch bei kleinen Betriebsspannungen gewährleistet, so daß bei  $U_0 = -0,1 V \dots +1,0 V$  mit  $U_s = \pm 5 V$  gearbeitet werden kann.

$$\begin{array}{c} R_{1} & R_{1} \\ u_{1} & 15k \\ 2,2 \\ z_{1} \\ z_{$$

Bild 37: Tiefpaß zur Brumnspannunterdrückung

Bild 37 zeigt ein Tiefpaßfilter, das zur Brummspännungsunterdrückung vor den High-Eingang (11) geschaltet werden kann. Mit  $R_1 = 15$  kOhm und  $C_1 = 2.2$  /uF ergibt sich eine Dämpfung von etwa 40 dB für 50 Hz, die für die meisten Fälle ausreichend sein wird. Der Vorsatz-OPV kann zusätzlich als Tiefpaß beschaltet werden. 8.7. Standardsignale und ihre Anpassung an den C 520 D

In der BMSR-Technik werden Standardsignale verwendet. Im folgenden wird die Anpassung des C 520 D an diese Signale gezeigt.

| Standard-<br>Signalbereiche | $\mathbb{R}_{L}$ (zwischen pin 10 und 11 )        |

|-----------------------------|---------------------------------------------------|

| 0 5 mA                      | 200 Ohm                                           |

| 0 10 mA                     | $100 \text{ Ohm}$ $U_{i_{max}} = 1000 \text{ mV}$ |

| 0 20mA                      | 50 Ohm                                            |

| 0                           | 20 Ohm                                            |

| 0 100 mA *                  | 10 Ohm                                            |

für große Entfernungen

| 0 | <br>1 | v | 1   |     | direkt | an | p; | in | 10 | und | 11  |

|---|-------|---|-----|-----|--------|----|----|----|----|-----|-----|

| 0 | <br>5 | v |     |     | Teiler | 5  | :  | 1  |    |     |     |

|   |       |   | - C | 1.1 | Teiler | 10 | :  | 1  |    |     | 143 |

Standardsignale

| mit Offset                | 90 S. | imax 1000 mV                  |

|---------------------------|-------|-------------------------------|

| $\mathbf{I}_{\mathbf{A}}$ | ΔI    | $R_{L} = \Delta I = \Delta I$ |

| 1 ••• 5 mA                | 4 mA  | 250 Ohm                       |

| 2 10 mA                   | 8 mA  | 125 Ohm                       |

| 4 20 mA                   | 16 mA | 62,5 Ohm                      |

Tabelle 9 ; Standardsignale der BMSR-Technik

Bei den Standardstromsignalen mit Offset ist der Anfangswert I<sub>A</sub> zu kompensieren. Bild 38 zeigt die Angaßschaltung. 79

Bild 38: Anpaßschaltung an Stromsignale mit Offset

Der Offsetwert wird durch die Spannung an  $R_2$ , die von der Stromquelle  $I_A$  erzeugt wird, kompensiert. Dabei ist zu beachten, daß der zulässige Gleichtaktbereich von  $\pm$  200 mV überschritten wird ( $U_{CM} = \pm$  250 mV). D.h., dem Anwender werden die Parameter des Wandlers nicht mehr garantiert. Im Abschnitt 6 sind dazu nähere Erläuterungen enthalten,

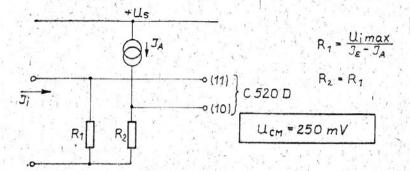

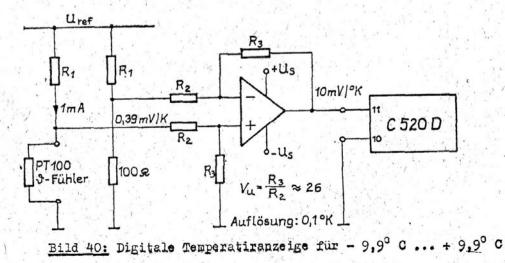

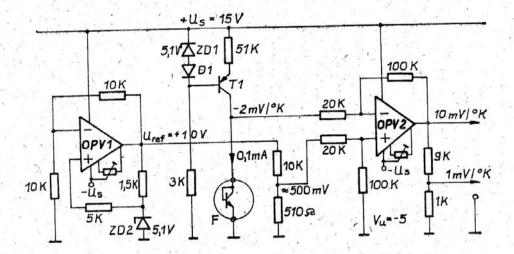

#### 8.8. Temperaturmessung

In der BMSR-Technik treten die wichtigsten analogen Meßgrößen bei technischen Prozessen in folgender typischer Verteilung auf /13/.

| Meßgröße             | Anteil [ | Kosten |

|----------------------|----------|--------|

| 1. Temperatur        | 50 %     | 1,6 %  |

| 2. Durchfluß, Menge  | 20 %     | . 22 % |

| 3. Druck             | 15 %     | 16 %   |

| 4. Fullstand, Niveau | 10 %     | 16 %   |

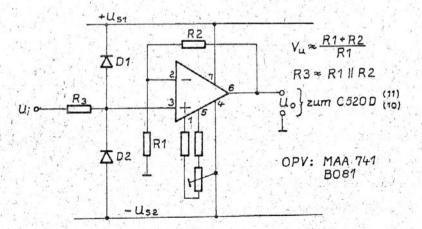

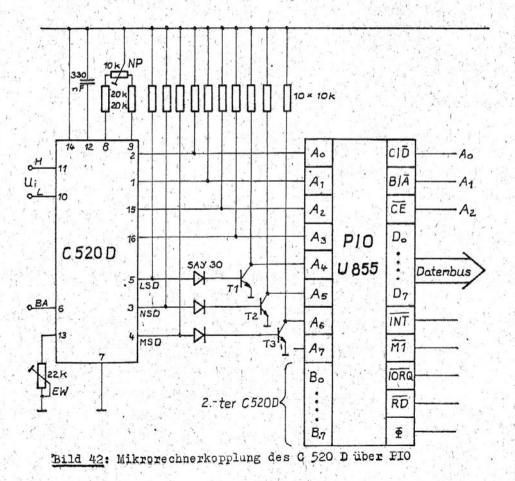

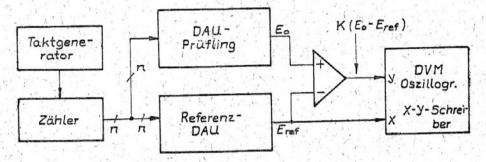

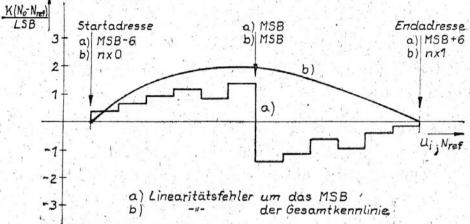

| 5. Stoffanalyse      | 5%       | 30,%   |